GeneSiC

## APPLICATION NOTE AN1003

# SiC Merged PiN-Schottky (MPS) Diodes SPICE Model Usage Instructions

## CONTENTS

| 1 | Electrical Model (Level-1) |

|---|----------------------------|

| 2 | Electrical Model (Level-3) |

| 3 | Installation               |

| 4 | Usage                      |

|   | Disclaimer                 |

**J**GeneSiC<sup>®</sup>

This application note provides information on installing and using GeneSiC Semiconductor's SPICE models. The SPICE model package for each part consists of:

- 1) Encrypted electrical model (L1) library file

- 2) Encrypted electro-thermal model (L3) library file (if applicable)

- 3) Symbol files (.asy) for L1 and L3 models

The following points should be noted by the user while using these SPICE models:

- The models are designed to be accurate over the ranges presented in the corresponding datasheet typical curves.

- The models are valid over the 25 °C to 175 °C operating range.

- The surge response of the PiN structure is included only in the electro-thermal models (L3) and may not accurately represent the typical high current characteristics.

- In case of dual diode packages (TO-247-3L and SOT-227), the models are per leg.

#### 1 – Electrical Model (Level-1)

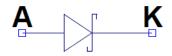

This model represents the typical electrical characteristics presented in the corresponding datasheet and does not account for the effects of self-heating. The junction temperature of this model can be set using the global temperature (.temp) LTSPICE variable. As evident in the SPICE symbol below, this model has two ports – Anode and Kathode.

#### 2 - Electro-Thermal Model (Level-3)

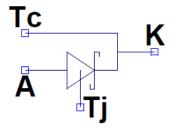

The Level-III model, often known as the self-heating electro-thermal model, includes the values of the internal thermal path to estimate the device temperature. This model provides a more realistic presentation of the device behavior.  $T_C$  represents the case temperature and the user can set its value by connecting a voltage source referenced to the thermal ground. The voltage measured at  $T_j$  estimates the internal temperature of the device and it should be noted that the absolute maximum temperature at  $T_j$  should not exceed 175 °C. The remaining two ports - Anode and Kathode, are connected into the electrical circuit. The thermal parameters of an external heat-sink may be included as a physical correct thermal RC network to the node  $T_C$  and referenced to the thermal ground.

## 3 – Installation

These instructions are for LTSPICE users and provide guidance on installing GeneSiC Semiconductor's SPICE symbols and model libraries on the user's system.

- After unzipping the package downloaded from the website, place the "GeneSiC Semiconductor" sub-folder containing SPICE symbols (.asy files) into the user's default LTSPICE symbols library directory. (Example Location: C:\Users\Admin\Documents\LTspiceXVII\lib\sym)

- Place the specific device model library file (.lib files) into a directory of the user's choice. Remember this path as it will be needed to enter into LTSPICE later. (Example Location: C:\Users\Admin\Documents\GeneSiC)

- Open or restart LTSPICE to load the new symbols.

## 4 – Usage

- Place the GeneSiC symbol (Example: L3\_GeneSiC\_MPS.asy) into the LTSPICE schematic using the Edit>Component selection dialog box.

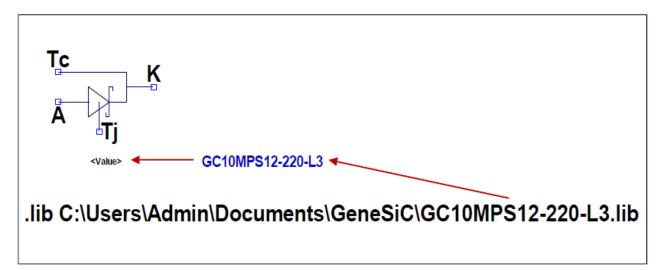

- Add a .lib SPICE directive which will link the relevant GeneSiC model library file to this schematic. Click Edit>SpiceDirective and a text box will appear. Enter the text ".lib C:\Users\Admin\Documents\GeneSiC\GC10MPS12-220-L3.lib" without the quotes and click OK to position the directive textbox anywhere on the schematic and then click to place it. It should be noted that the path of the library file should be accurately represented.

- Right Click on the newly placed GeneSiC component and edit the Value attribute. Update the value of this attribute to the title of the library file (Example: *GC10MPS12-220-L3*)

- The same symbol can be used for all similar GeneSiC parts in case the user wants to switch between different GeneSiC parts. In such cases, the "Value" attribute and .lib SPICE directive should be addressed accordingly. The figure shown explains this step.

### Disclaimer

Models provided by GeneSiC Semiconductor are not warranted as fully representing all of the specifications and operating characteristics of the product to which the model relates. The model describes the characteristics of a typical product, and in all cases, the most recent revision of the product's datasheet is the final design guideline and the only actual performance specification. Although SPICE models can be a useful tool in evaluating device performance, they cannot model the exact device performance under all conditions, nor are they intended to replace the design verification process. Therefore, GeneSiC Semiconductor does not assume any liability arising from their use and reserves the right to change models without prior notice.

#### Additional Information

DISCLAIMER Navitas Semiconductor (Navitas) reserves the right to modify the products and/or specifications described herein at any time and at Navitas' sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied. This document is presented only as a guide and does not convey any license under intellectual property rights of Navitas or any third parties. Navitas' products are not intended for use in applications involving extreme environmental conditions or in life support systems. Terms and Conditions.

Navitas, GaNFast, GaNSense, GeneSiC, and the Navitas logo are trademarks or registered trademarks of Navitas Semiconductor and subsidiaries. All other brands, product names, and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners.

Copyright ©2023 Navitas Semiconductor. All rights reserved. Contact: info@navitassemi.com