# **Navitas**

# **GaN Power ICs:**

### **Device Integration Delivers Application Performance**

5th IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA) Albuquerque, NM, USA. November 1<sup>st</sup> 2017

MHz 40MHz 50MHz 1MHz 10MHz 20MHz 30MHz 40MHz 50MHz 1MHz 10MHz 20MHz 30MHz 40MHz 50MHz 1MHz 10MHz Dr. Nick Fichtenbaum, Co-Founder & VP Engineering

Nick.Fichtenbaum@navitassemi.com

Navitas GaN Power IC Navitas GaN Power

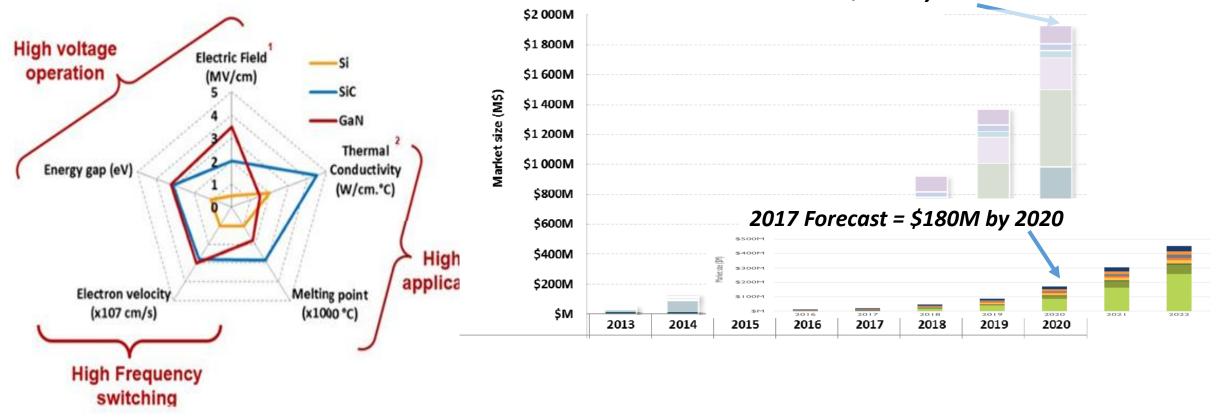

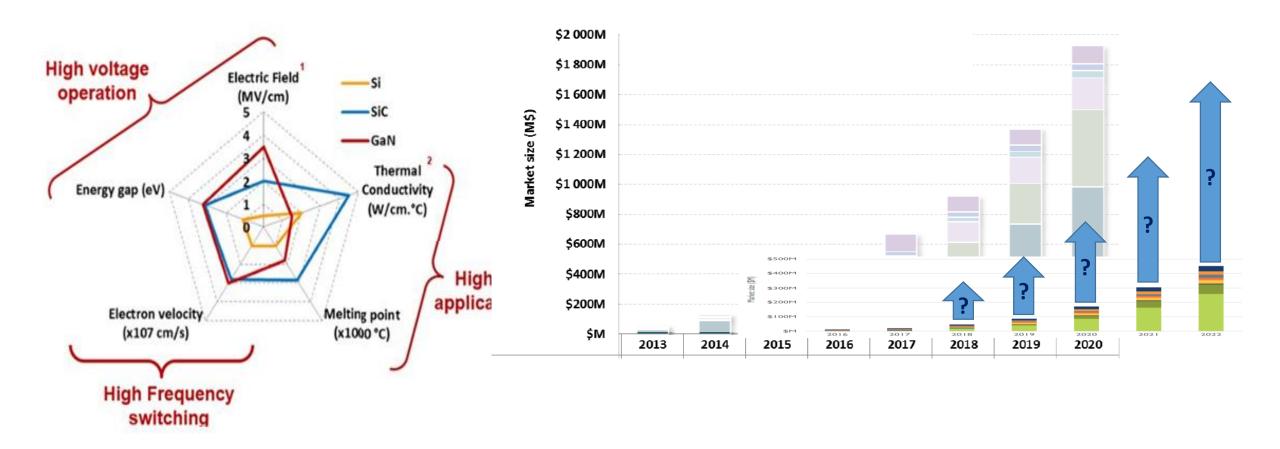

### Fast GaN, Slow Adoption?

2012 Forecast = \$1.9B by 2020!

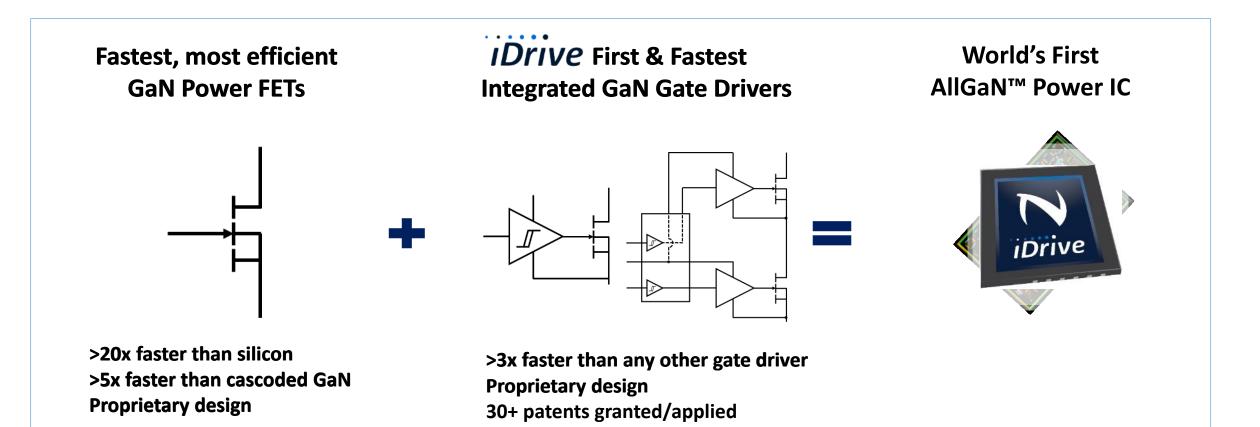

### Faster with AllGaN<sup>™</sup> Integration!

3

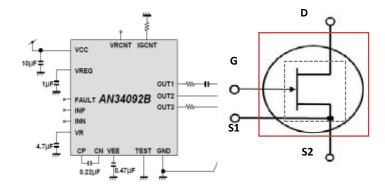

# World's First AllGaN<sup>™</sup> Power ICs

Up to 40MHz switching, 5x higher density & 20% lower system cost

Navitas

### The Drive for **Better Drivers**

- Low V<sub>TH</sub>

- Low R x Q •

- $\mathsf{Low} \ \mathsf{V}_{\mathsf{GS}\_\mathsf{Max}}$ •

#### Discrete FET + Discrete Driver

| Gate Drive Challenges           | Discrete<br>FET<br>+<br>Discrete<br>Driver | Discrete<br>FET<br>+<br>Custom<br>driver | GaN<br>Power IC | łS |

|---------------------------------|--------------------------------------------|------------------------------------------|-----------------|----|

| Eliminate Gate Oscillations     |                                            |                                          |                 |    |

| Eliminate dV/dt Induced Turn-on | $\checkmark$                               |                                          |                 |    |

| Regulate Gate Drive Voltage     | $\checkmark$                               |                                          |                 |    |

| Gate Overvoltage Protection     | $\checkmark$                               |                                          |                 |    |

| Reduce Design Complexity        | ×                                          |                                          |                 |    |

| Manage Noise Sensitivity        | ×                                          |                                          |                 |    |

| Fast Turn-on/off Speed          | ×                                          |                                          |                 |    |

| Gate ESD Protection             |                                            |                                          |                 |    |

| Layout Insensitive              | ×<br>×<br>×<br>×<br>×                      |                                          |                 |    |

| Lowest PCB Area                 | ×                                          |                                          |                 |    |

| Lowest Cost                     | ×                                          |                                          |                 |    |

| Remove Negative Drive           | ×                                          |                                          |                 |    |

| Fast Start-up                   |                                            |                                          |                 |    |

| Eliminate Standby Loss          | $\checkmark$                               |                                          |                 |    |

|                                 |                                            |                                          |                 | 6  |

### The Drive for **Better Drivers**

- Low V<sub>TH</sub>

- Low R x Q •

- Low V<sub>GS\_Max</sub>

#### Discrete FET + Custom Driver

| Gate Drive Challenges           | Discrete<br>FET<br>+<br>Discrete<br>Driver | Discrete<br>FET<br>+<br>Custom<br>driver | GaN<br>Power IC | ìS |

|---------------------------------|--------------------------------------------|------------------------------------------|-----------------|----|

| Eliminate Gate Oscillations     |                                            |                                          |                 |    |

| Eliminate dV/dt Induced Turn-on | $\checkmark$                               | $\checkmark$                             |                 |    |

| Regulate Gate Drive Voltage     | $\checkmark$                               | $\checkmark$                             |                 |    |

| Gate Overvoltage Protection     | $\checkmark$                               | $\checkmark$                             |                 |    |

| Reduce Design Complexity        | ×                                          | $\checkmark$                             |                 |    |

| Manage Noise Sensitivity        | ×                                          | $\checkmark$                             |                 |    |

| Fast Turn-on/off Speed          | ×                                          | $\sim$                                   |                 |    |

| Gate ESD Protection             | ×                                          | ×                                        |                 |    |

| Layout Insensitive              | ×                                          | ×                                        |                 |    |

| Lowest PCB Area                 | ×                                          | ×                                        |                 |    |

| Lowest Cost                     | ×                                          | ×                                        |                 |    |

| Remove Negative Drive           | ×                                          | ×                                        |                 |    |

| Fast Start-up                   |                                            | ×                                        |                 |    |

| Eliminate Standby Loss          | $\checkmark$                               | ×                                        |                 | 7  |

### The Drive for Better Drivers

- Low V<sub>TH</sub>

- Low R x Q

- Low V<sub>GS\_Max</sub>

#### GaN Power IC

No compromises

| Gate Drive Challenges           | Discrete<br>FET<br>+<br>Discrete<br>Driver | Discrete<br>FET<br>+<br>Custom<br>driver | GaN<br>Power IC | ÌS |

|---------------------------------|--------------------------------------------|------------------------------------------|-----------------|----|

| Eliminate Gate Oscillations     |                                            |                                          |                 |    |

| Eliminate dV/dt Induced Turn-on | $\checkmark$                               | $\checkmark$                             | $\checkmark$    |    |

| Regulate Gate Drive Voltage     | $\checkmark$                               | $\checkmark$                             | $\checkmark$    |    |

| Gate Overvoltage Protection     | $\checkmark$                               | $\checkmark$                             | $\checkmark$    |    |

| Reduce Design Complexity        | ×                                          | $\checkmark$                             | $\sim$          |    |

| Manage Noise Sensitivity        | ×                                          | $\checkmark$                             | $\checkmark$    |    |

| Fast Turn-on/off Speed          | ×                                          | $\checkmark$                             | $\sim$          |    |

| Gate ESD Protection             | ×                                          | ×                                        | $\checkmark$    |    |

| Layout Insensitive              | ×                                          | ×                                        | $\sim$          |    |

| Lowest PCB Area                 | ×                                          | ×                                        | $\checkmark$    |    |

| Lowest Cost                     | ×                                          | ×                                        | $\sim$          |    |

| Remove Negative Drive           | ×                                          | ×                                        | $\checkmark$    |    |

| Fast Start-up                   |                                            | ×                                        |                 |    |

| Eliminate Standby Loss          | $\checkmark$                               | ×                                        |                 |    |

|                                 |                                            |                                          |                 | 0  |

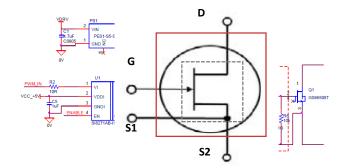

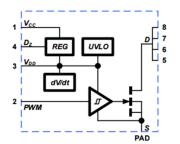

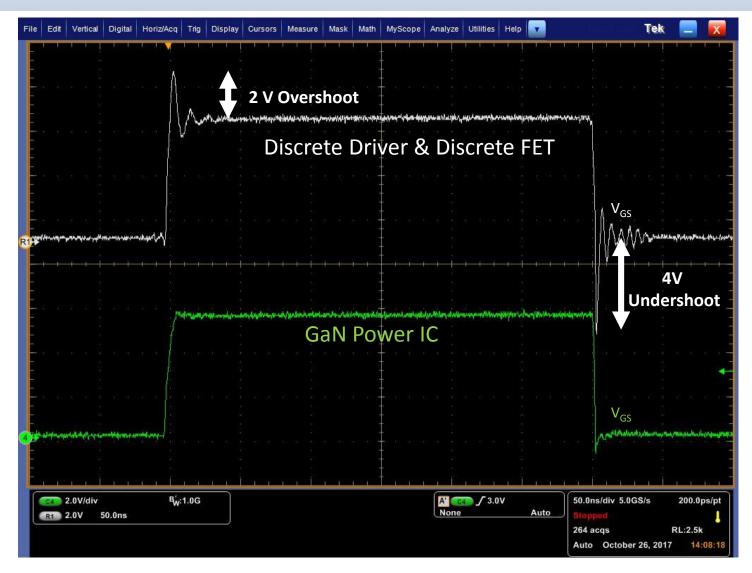

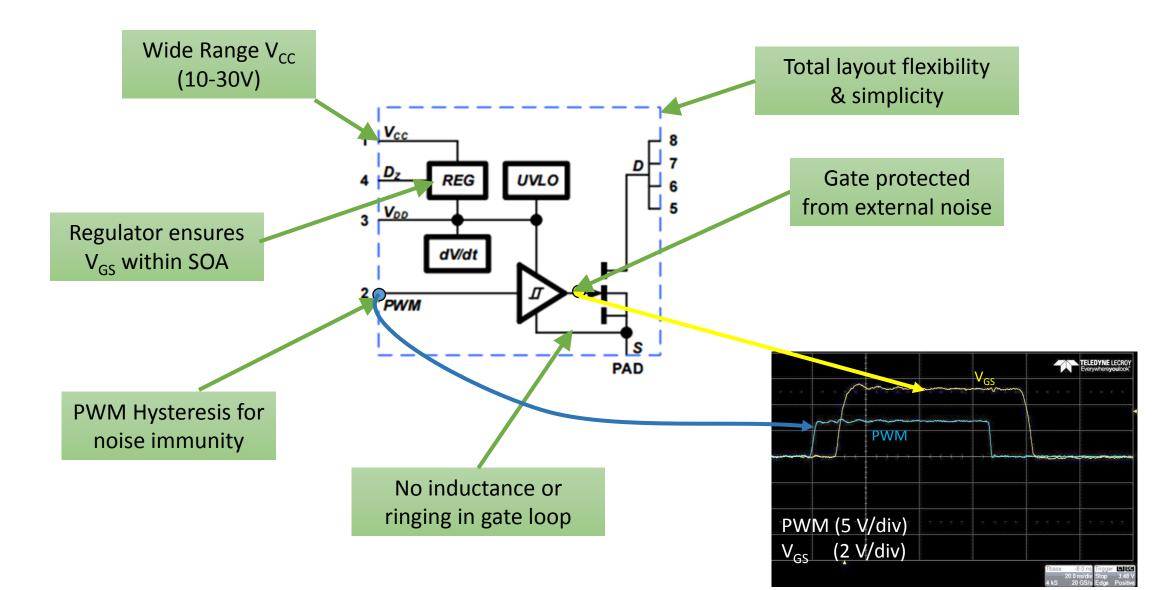

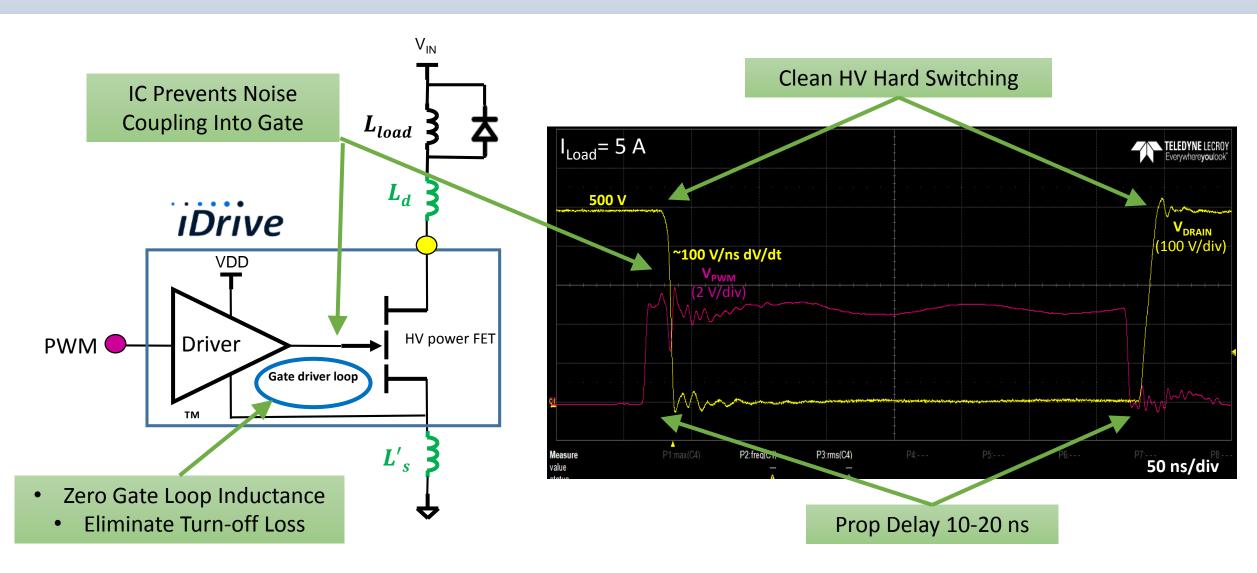

# **Clean, Controlled FET Gate**

#### • Discrete driver

- Gate loop inductance creates overshoot (even with good layout)

- Reliability concern

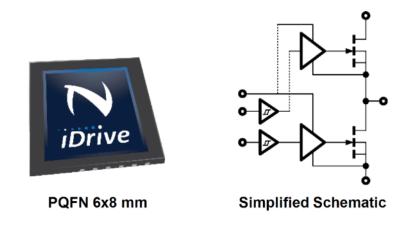

#### • iDrive<sup>™</sup> GaN Power IC

- No gate loop parasitic

- Clean and fast gate signal

## Integrated Drive -> Simple & Robust

9

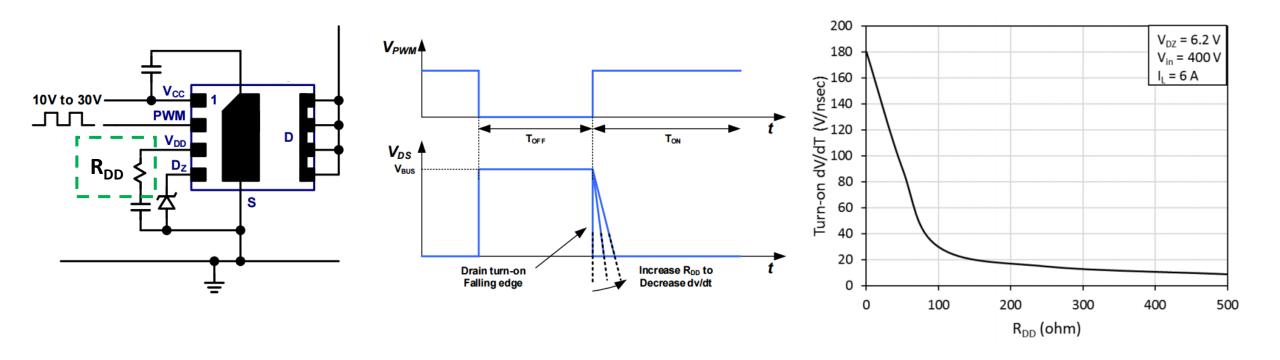

# Fast & Clean Hard Switching

#### **Voltage Slew-Rate Control ... Easy EMI Tuning**

dV/dt controllable from 180 V/ns to 10 V/ns

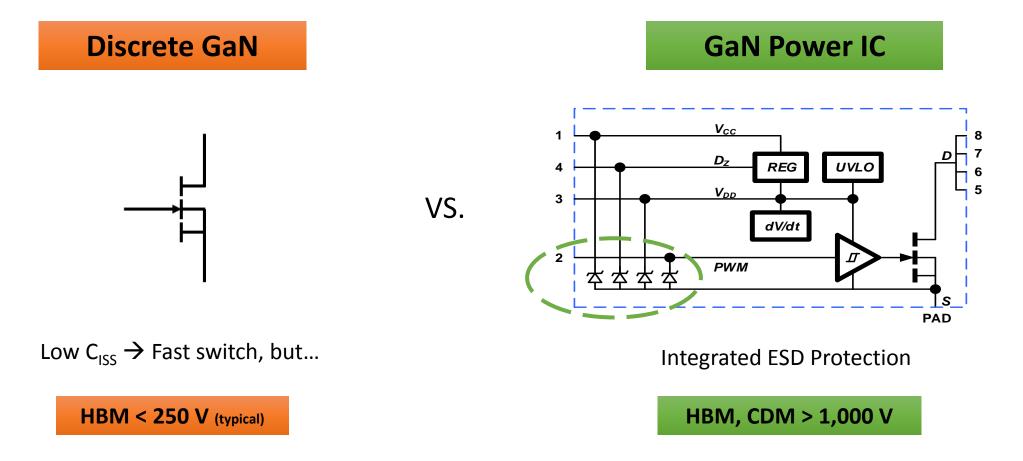

### **ESD Protection?**

### Using Integration to Improve Power Density

**Navitas**

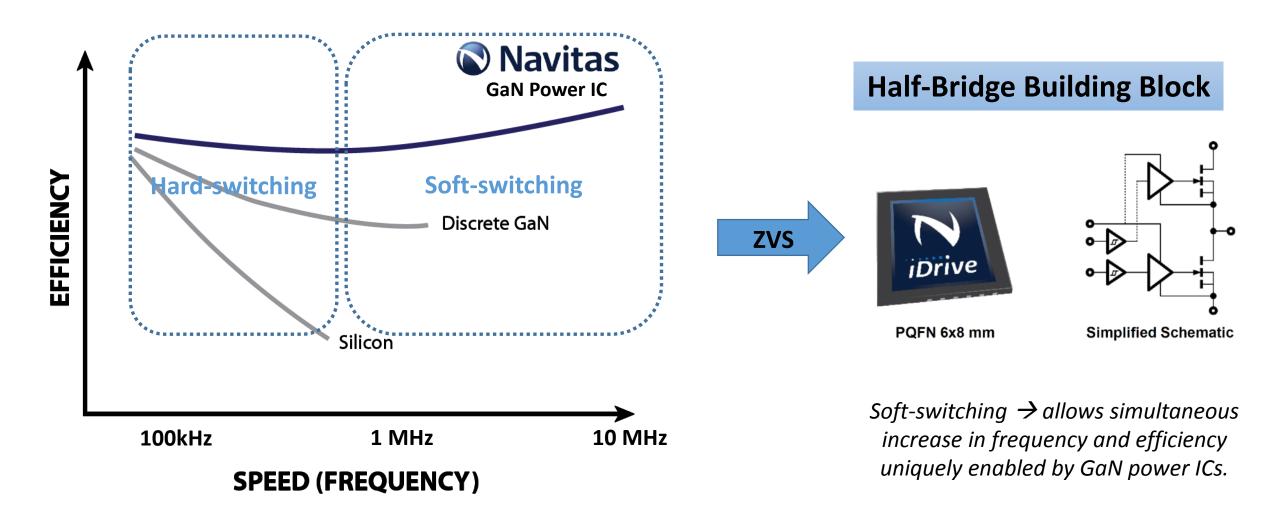

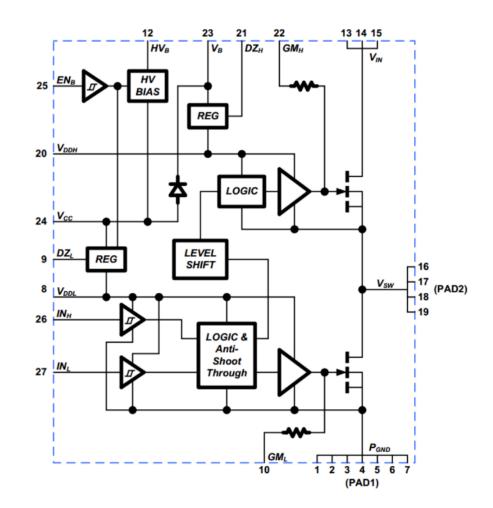

# **High-Frequency Half-Bridge Integration**

I/FOn-chipGate DriverChipTransformerChipSi CMOSSiO2 / PolyimideSi CMOS

Bootstrap Diode Si / SiC Half-Bridge FETs Si

#### **Disparate Technologies**

Hybrid isolator, discrete driver, discrete power, bootstrap diode

#### **High Power Loss**

- Driver loss, R<sub>G</sub> loss

- Bootstrap diode Q<sub>RR</sub>, V<sub>F</sub>

- Pulsed high current level shifter power (?)

**Monolithic Platform** Lateral GaN-on-Si, Half-Bridge GaN Power IC

#### Low Power Loss

- No gate driver loop parasitics, matched driver-FET capability, negligible loss vs frequency

- Zero Q<sub>RR</sub>, low V<sub>DS</sub> in synchronous charging

- Extremely fast, low-power level-shifter, multi-MHz operation, short propagation delay

# Simple, Powerful, Efficient, Cost-Effective

- Internal level-shift & bootstrap circuits

- Monolithic integration

- Single component

- Ground-referenced control

- Active Clamp Flyback, Half-Bridge, LLC, etc.

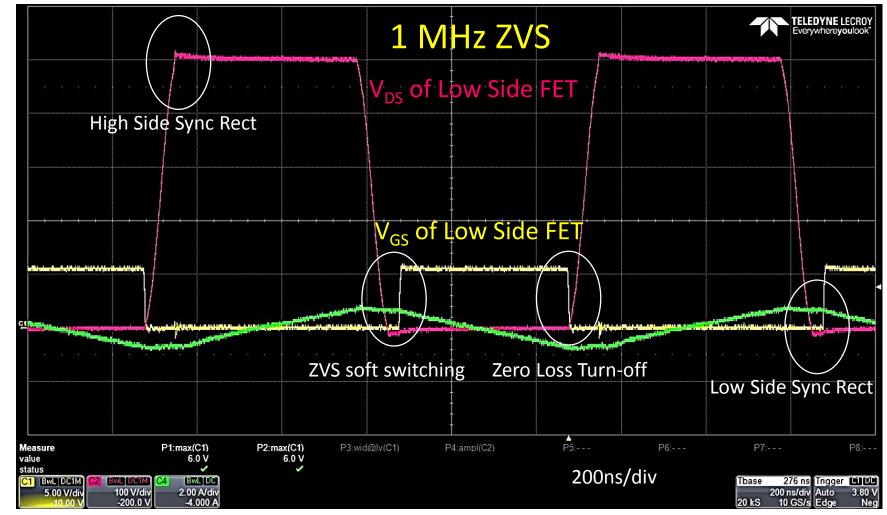

# GaN Power IC – Fast & Efficient

- 500 V Switching

- No overshoot / spike

- No oscillations

- 'S-curve' transitions

- Zero Loss Turn-on

- Zero Loss Turn-off

- Sync Rectification

- High frequency

- Small, low cost magnetics

## Complex Design → Made Simple

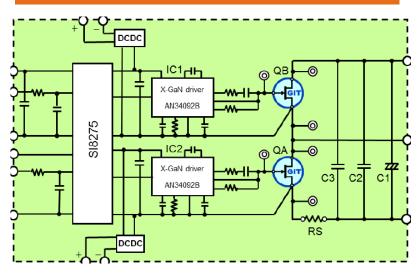

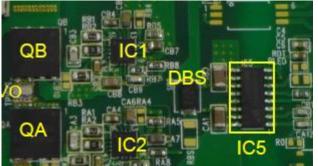

#### Half-Bridge Discrete GaN

PCB Area: 24 x 42 ~ 1,000 mm<sup>2</sup>

#### Half-Bridge GaN Power IC

✓ 20x smaller PCB area

✓ Robust & protected

$\checkmark$  Lower cost

✓ Easy layout

✓ Simple

$\checkmark$  40+ fewer components

#### PCB Area: $6 \times 8 = 48 \text{ mm}^2$

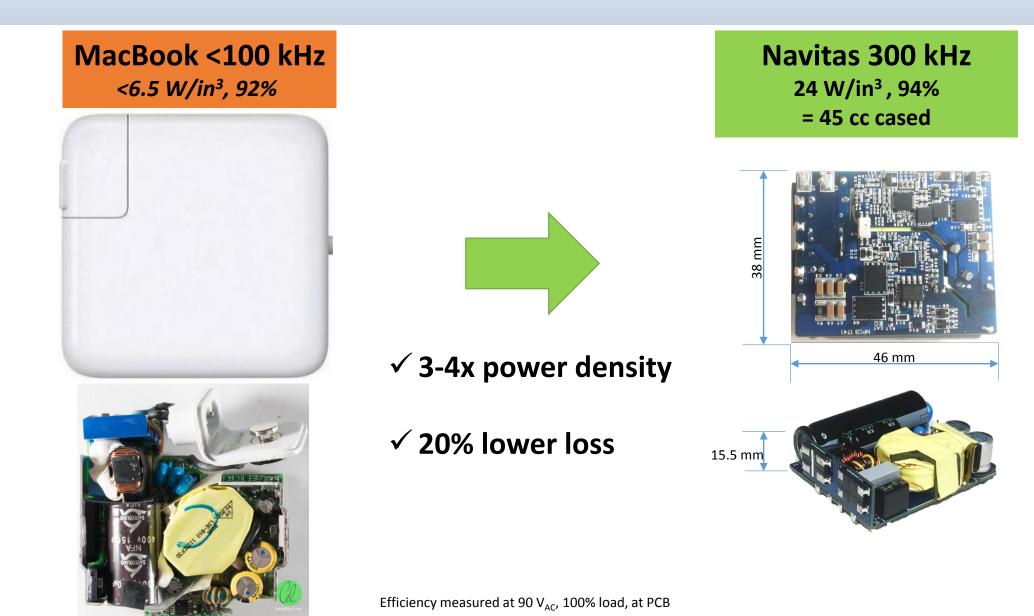

#### The World's Smallest 65W USB-PD Adapter

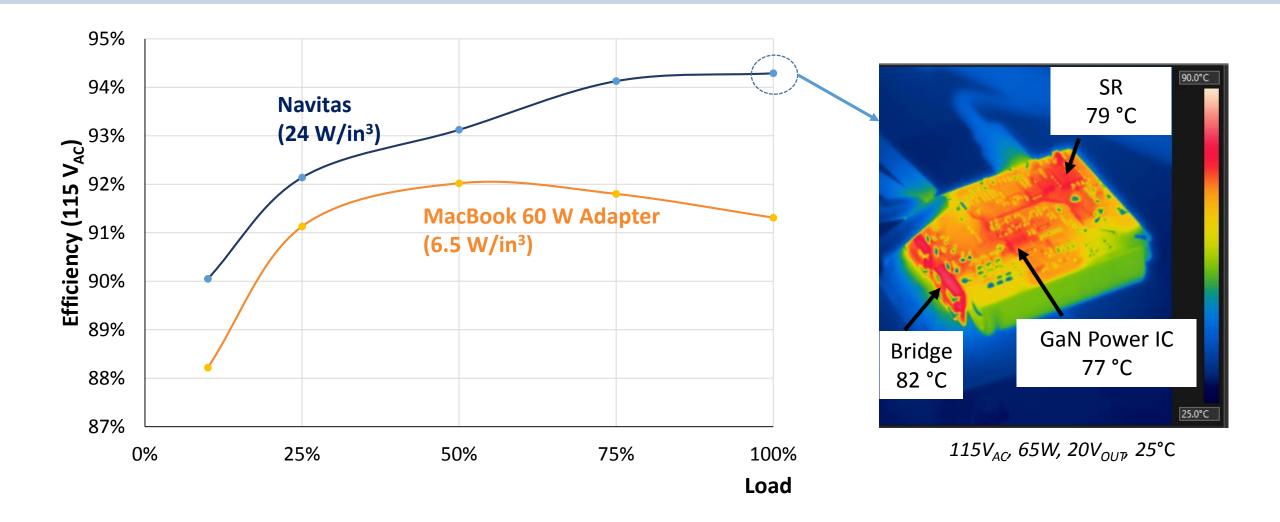

## **Best-in-Class Efficiency, Cool Operation**

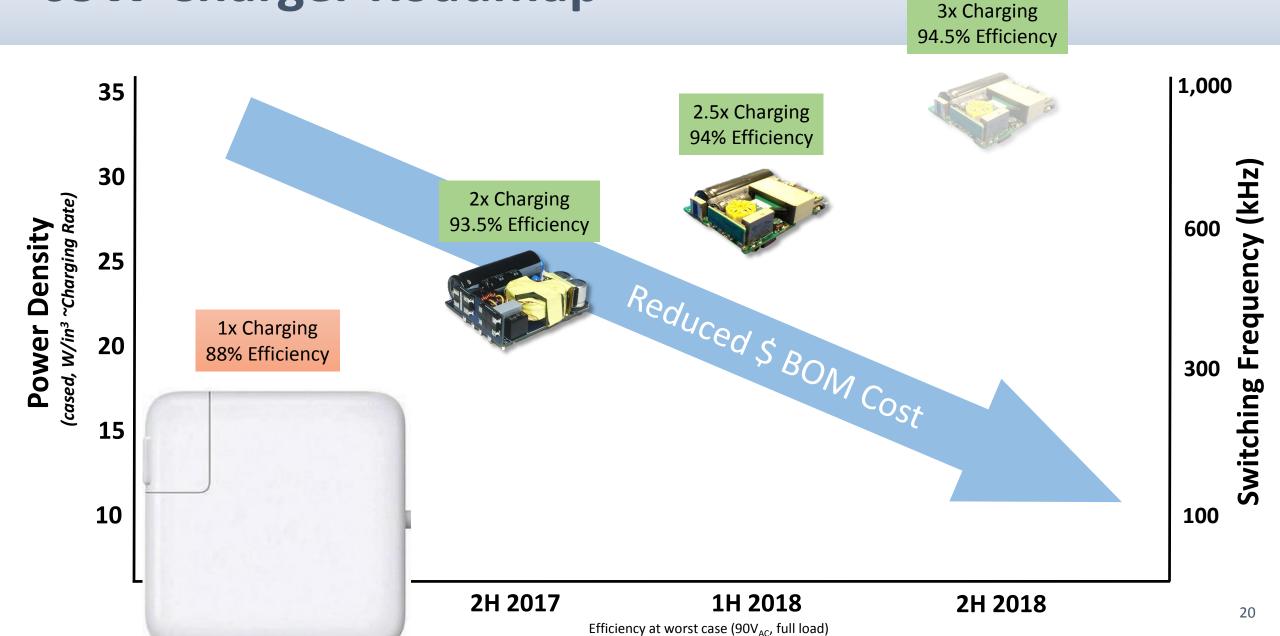

### 65W Charger Roadmap

# **Navitas**

# **GaN Power ICs:**

### **Device Integration Delivers Application Performance**

5th IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA) Albuquerque, NM, USA. November 1<sup>st</sup> 2017

MHz 40MHz 50MHz 1MHz 10MHz 20MHz 30MHz 40MHz 50MHz 1MHz 10MHz 20MHz 30MHz 40MHz 50MHz 1MHz 10MHz Dr. Nick Fichtenbaum, Co-Founder & VP Engineering

Nick.Fichtenbaum@navitassemi.com

Navitas GaN Power IC Navitas GaN Power