## **77TH DEVICE RESEARCH CONFERENCE**

June 23-26, 2019 // University of Michigan, Ann Arbor // Ann Arbor, MI

# Navitas Let's go GaNFast™

DRC

## **GaN Power Integrated Circuits**

Dr. Nick Fichtenbaum, Co-Founder & VP Engineering

Nick.Fichtenbaum@navitassemi.com

- Why GaN Power ICs

- How to make GaN Power ICs

- Features of GaN Power ICs

- Commercial requirements for GaN products

- Products using GaN Power ICs

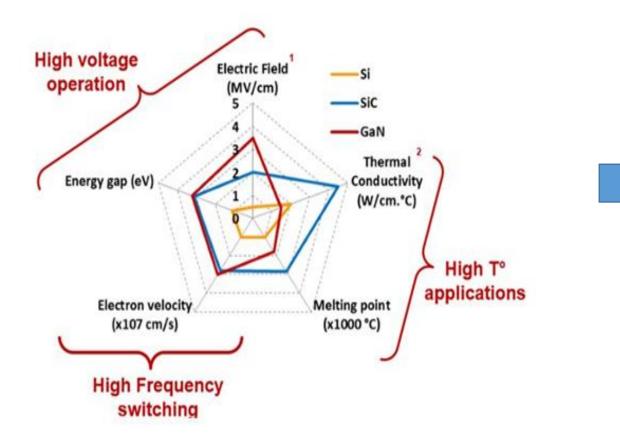

## **Potential of GaN Power Devices**

#### **Important Material Attributes**

**System Benefits**

✓ Efficiency

✓ Cost Savings

✓ Power Density

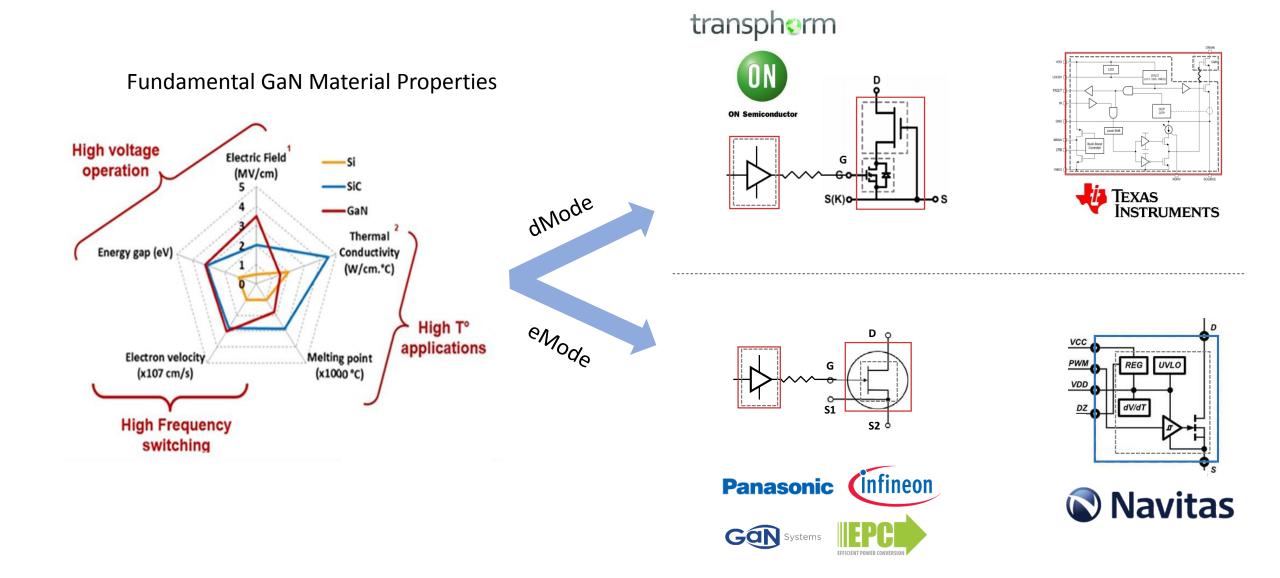

## **Unlocking GaN's Value**

## World's First GaN Power ICs

Fastest, most efficient GaN Power FETs First & Fastest Integrated GaN Gate Drivers World's First GaNFast Power ICs

>20x faster than silicon>5x faster than cascoded GaNProprietary design

>3x faster than any other gate driverProprietary design75+ patents granted/applied

Up to 5x higher density & 20% lower system cost

## **The Drive for Better Drivers**

- Low  $V_{TH}$ •

- Low R x Q •

- Low  $V_{GS\_Max}$ •

#### Discrete FET + Discrete Driver

| Gate Drive Challenges           | Discrete<br>FET<br>+<br>Discrete<br>Driver | Discrete<br>FET<br>+<br>Custom<br>driver | GaN<br>Power IC | TM |

|---------------------------------|--------------------------------------------|------------------------------------------|-----------------|----|

| Eliminate Gate Oscillations     |                                            |                                          |                 |    |

| Eliminate dV/dt Induced Turn-on | $\checkmark$                               |                                          |                 |    |

| Regulate Gate Drive Voltage     |                                            |                                          |                 |    |

| Gate Overvoltage Protection     | $\checkmark$                               |                                          |                 |    |

| Reduce Design Complexity        | ×                                          |                                          |                 |    |

| Manage Noise Sensitivity        | ×                                          |                                          |                 |    |

| Fast Turn-on/off Speed          | ×                                          |                                          |                 |    |

| Gate ESD Protection             | ×                                          |                                          |                 |    |

| Layout Insensitive              | ×                                          |                                          |                 |    |

| Lowest PCB Area                 | ×                                          |                                          |                 |    |

| Lowest Cost                     | ×                                          |                                          |                 |    |

| Remove Negative Drive           | ×                                          |                                          |                 |    |

| Fast Start-up                   |                                            |                                          |                 |    |

| Eliminate Standby Loss          | $\checkmark$                               |                                          |                 |    |

|                                 |                                            |                                          |                 | 6  |

## The Drive for Better Drivers

- Low V<sub>TH</sub>

- Low R x Q

- Low V<sub>GS\_Max</sub>

#### Discrete FET + Custom Driver

| Gate Drive Challenges           | Discrete<br>FET<br>+<br>Discrete<br>Driver | Discrete<br>FET<br>+<br>Custom<br>driver | GaN<br>Power IC | TM |

|---------------------------------|--------------------------------------------|------------------------------------------|-----------------|----|

| Eliminate Gate Oscillations     |                                            |                                          |                 |    |

| Eliminate dV/dt Induced Turn-on | $\checkmark$                               | $\checkmark$                             |                 |    |

| Regulate Gate Drive Voltage     | $\checkmark$                               | $\checkmark$                             |                 |    |

| Gate Overvoltage Protection     | $\checkmark$                               | $\checkmark$                             |                 |    |

| Reduce Design Complexity        | ×                                          | $\checkmark$                             |                 |    |

| Manage Noise Sensitivity        | ×                                          | $\checkmark$                             |                 |    |

| Fast Turn-on/off Speed          | ×                                          | $\checkmark$                             |                 |    |

| Gate ESD Protection             |                                            | ×                                        |                 |    |

| Layout Insensitive              | ××                                         | ×                                        |                 |    |

| Lowest PCB Area                 | ×                                          | ×                                        |                 |    |

| Lowest Cost                     | ×                                          | ×                                        |                 |    |

| Remove Negative Drive           | ×                                          | ×                                        |                 |    |

| Fast Start-up                   |                                            | ×                                        |                 |    |

| Eliminate Standby Loss          | $\checkmark$                               | ×                                        |                 | 7  |

## The Drive for Better Drivers

- Low V<sub>TH</sub>

- Low R x Q

- Low V<sub>GS\_Max</sub>

#### GaN Power IC

#### No compromises

| Gate Drive Challenges           | Discrete<br>FET<br>+<br>Discrete<br>Driver | Discrete<br>FET<br>+<br>Custom<br>driver | GaN TA<br>Power IC |

|---------------------------------|--------------------------------------------|------------------------------------------|--------------------|

| Eliminate Gate Oscillations     |                                            |                                          |                    |

| Eliminate dV/dt Induced Turn-on | $\checkmark$                               | $\checkmark$                             | $\checkmark$       |

| Regulate Gate Drive Voltage     |                                            | $\checkmark$                             | $\checkmark$       |

| Gate Overvoltage Protection     | $\checkmark$                               | $\checkmark$                             | $\checkmark$       |

| Reduce Design Complexity        | ×                                          | $\checkmark$                             | $\checkmark$       |

| Manage Noise Sensitivity        | ×                                          | $\checkmark$                             | $\checkmark$       |

| Fast Turn-on/off Speed          | ×                                          | $\checkmark$                             | $\sim$             |

| Gate ESD Protection             | ×                                          | ×                                        | $\checkmark$       |

| Layout Insensitive              | ×                                          | ×                                        | $\checkmark$       |

| Lowest PCB Area                 | ×                                          | ×                                        | $\checkmark$       |

| Lowest Cost                     | ×                                          | ×                                        | $\sim$             |

| Remove Negative Drive           | ×                                          | ×                                        | $\checkmark$       |

| Fast Start-up                   |                                            | ×                                        | $\sim$             |

| Eliminate Standby Loss          | $\checkmark$                               | ×                                        | $\checkmark$       |

|                                 |                                            |                                          | 8                  |

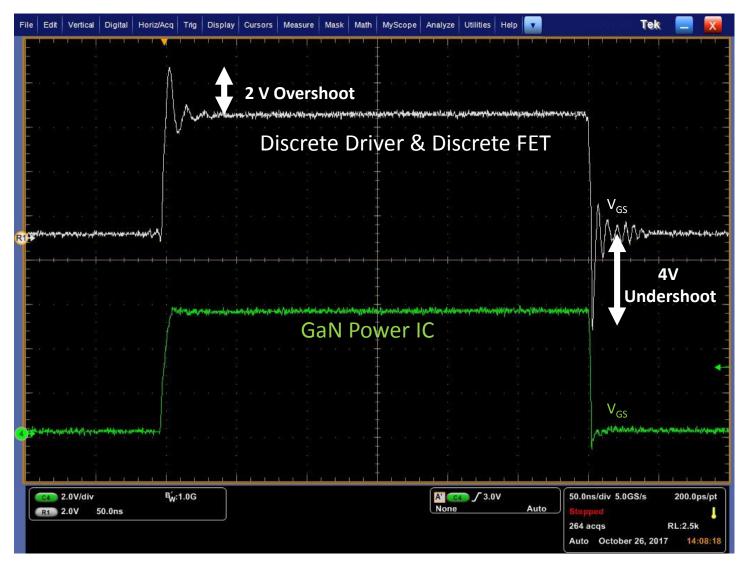

## Clean, Controlled, Easy to Use

#### Discrete driver

- Gate loop inductance creates overshoot (even with good layout)

- Reliability concern

### • GaNFast<sup>™</sup> GaN Power IC

- No gate loop parasitic

- Clean and fast gate signal

- GaNFast ICs unlock the <u>efficiency, cost, and power</u> <u>density of GaN</u> while making the customer experience <u>easy</u> <u>to use</u> and <u>reliable</u>

**GaNFast**<sup>™</sup>

- Why GaN Power IC?

- How to make GaN Power ICs?

- Features of GaN Power ICs

- Commercial requirements for GaN products

- Products using GaN Power ICs

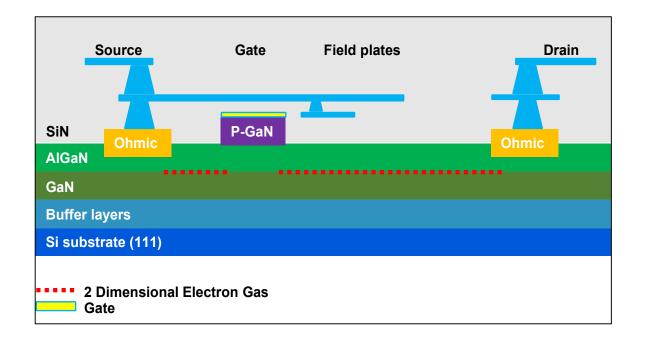

## **Navitas eMode Power FET Technology**

- Lateral device technology  $\rightarrow$  Convenient isolation and easy voltage scaling

- High breakdown field (10X) and high mobility (2X)  $\rightarrow$  Low R<sub>DS(ON)</sub>, Low Q<sub>OSS</sub>

- Lateral device technology  $\rightarrow$  Low Q<sub>G</sub>, easy to drive, easy to integrate

- Third quadrant operation, ie: bidirectional current flow, zero reverse recovery

- Processed in established CMOS line  $\rightarrow$  High yield, high capacity

- Multiple metal technology using standard CMOS processing equipment

## Navitas' Unique Characteristics: Fabless with its own PDK

GaN HEMT is still an emerging technology in the market.

- → Majority of GaN technologies and products developed are for high-voltage/power applications.

- → Also, GaN devices are only available in unipolar n-type.

Navitas team has strong knowledge and capability to develop its own device and circuit libraries even with such handicaps.

## **Power IC Models / PDK**

**GaNFast**™

- Excellent process design kit:

- Device symbols

- Pcells for automated device construction

- Scalable, accurate

- Verified for schematic and layout rules

- Layout parameter extraction

- Angelov, ASM and silicon models are not suitable

- Lack dMode, scalability, flexibility, speed

- Navitas GaN eMode FET scalable VerilogA model

- Flexible: customized features/equations

- High correlation between simulation and product

- High-speed simulations

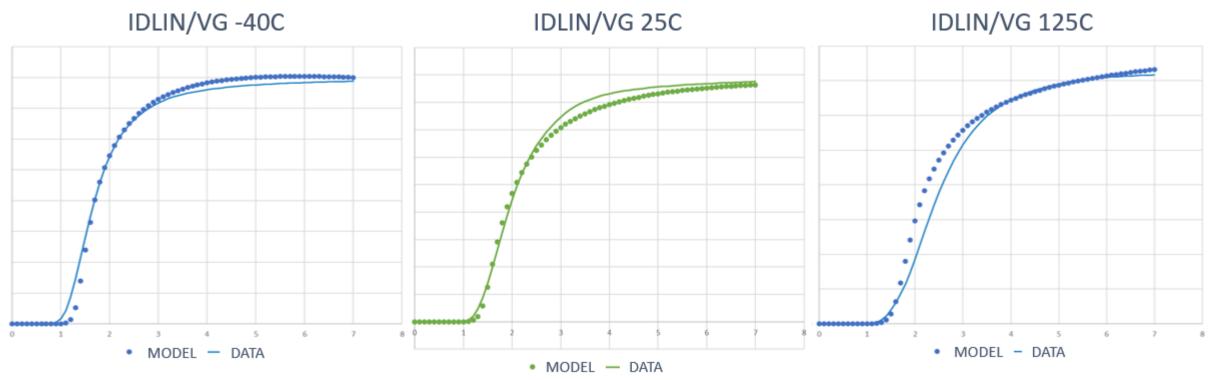

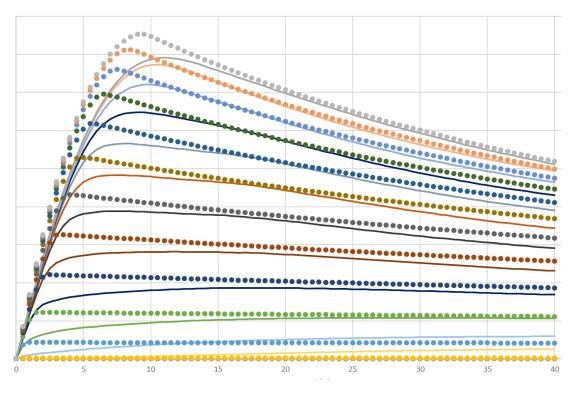

## **Accurate over Temperature**

#### • GaN FET I<sub>D</sub>V<sub>G</sub> Model with Temperature Effects

• Solid lines = measured, dotted lines = Cadence simulation

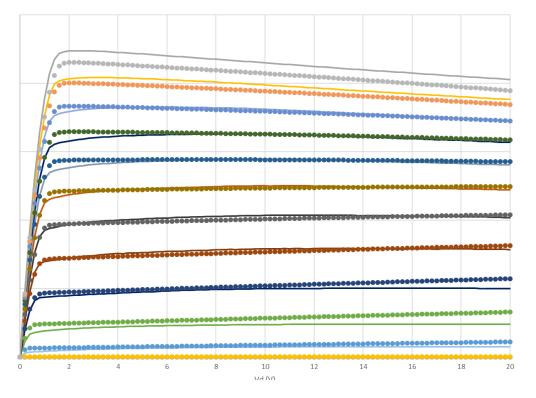

## **Accurate over Drain Voltage**

- Solid lines = measured, dotted lines = Cadence Spectre

- 20V rated eMode FET

#### 650V rated eMode FET

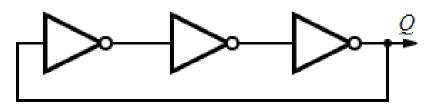

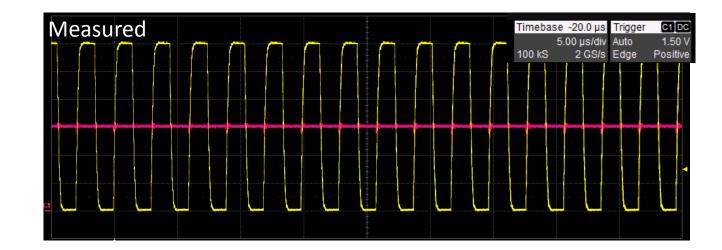

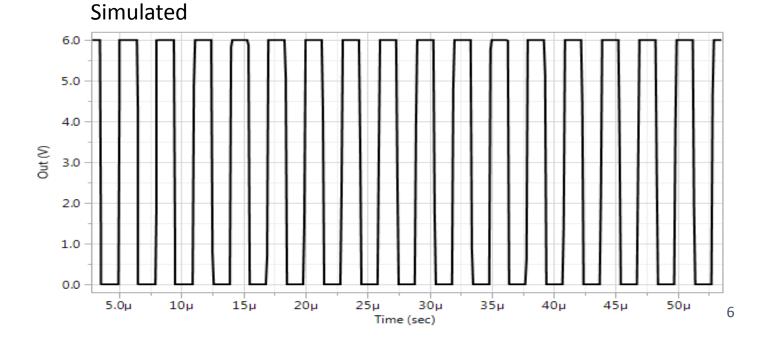

## **PDK Verification**

**Ring Oscillator**

- Use simple ring oscillator structure to verify accuracy of PDK models

- Excellent agreement between simulated and measured performance

- Needs to include parasitic effects

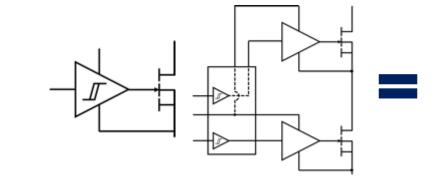

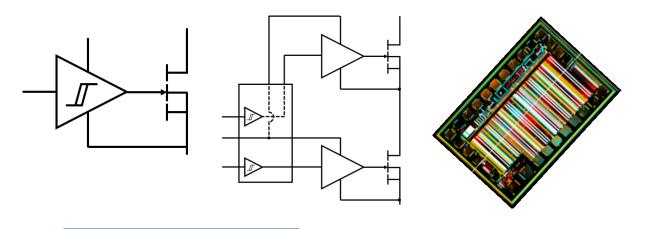

## Navitas GaNFast<sup>™</sup> IC Platform

#### First & Fastest Integrated GaN Gate Drivers

#### Navitas GaN IC PDK

- PDK developed independent of the foundry

- Offers great deal of design flexibility

- Fast design/tape out cycle time

- Enables seamless integration of new devices and features

- Scalable models, streamlined for process corners

#### **Navitas Proprietary GaN Building Blocks**

- eMode and dMode transistors (7V 650V)

- Integrated capacitors (7V 650V)

- Integrated resistors

- Inverters

- Buffers

- Logic gates

- Pulse generators

- Level shifters

- ESD I/O circuits

- Why GaN Power IC?

- How to make GaN Power ICs?

- Features of GaN Power ICs

- Commercial requirements for GaN products

- Products using GaN Power ICs

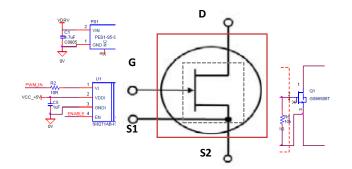

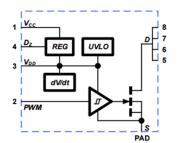

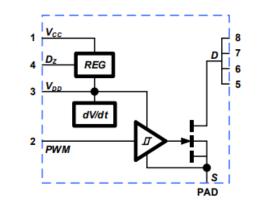

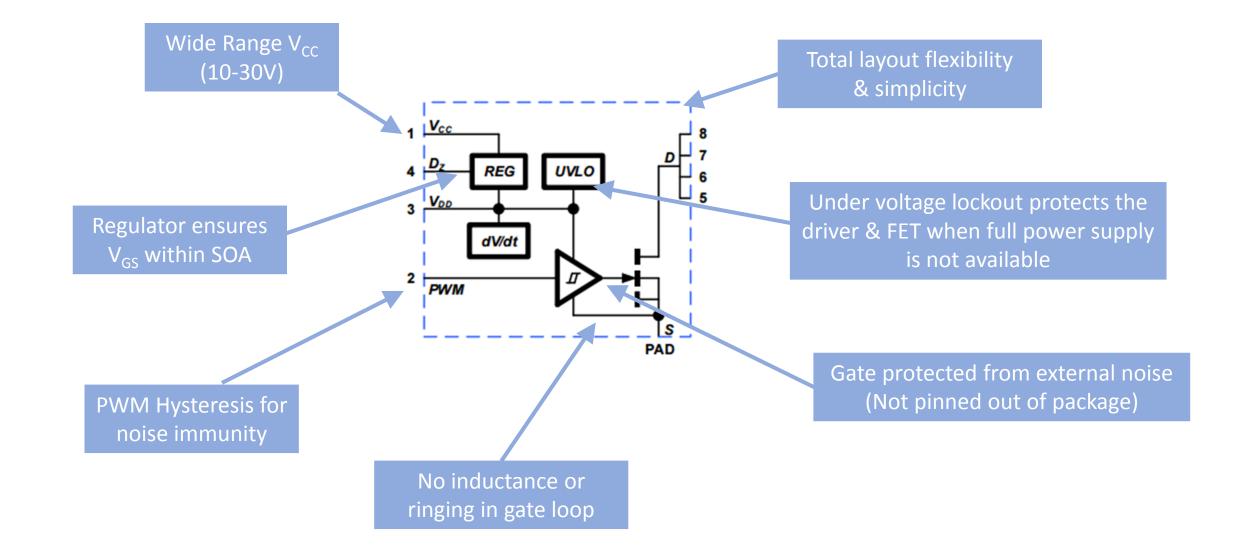

## **Power GaN IC Product Portfolio**

#### Single Switch ("Singles")

- ✓ 650 V eMode FET

- ✓  $R_{DS(ON)}$  120-300m $\Omega$  available

- ✓ Integrated Gate Drive

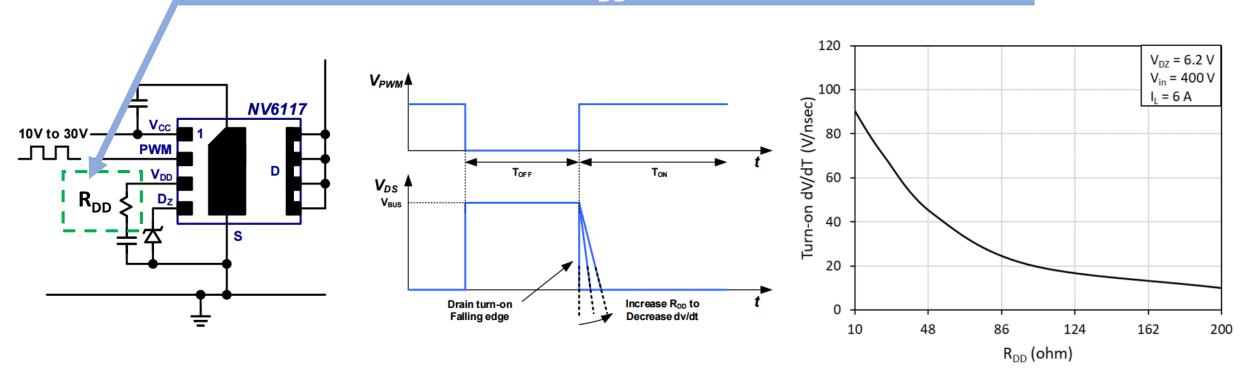

- ✓ Programmable dv/dt Control

- ✓ Integrated Regulator

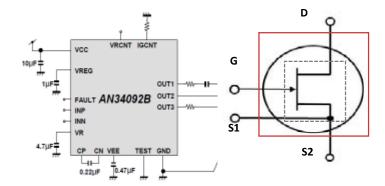

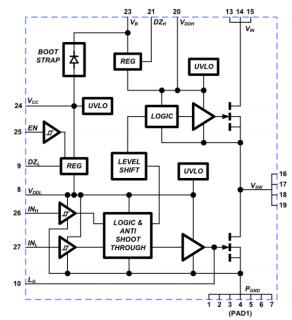

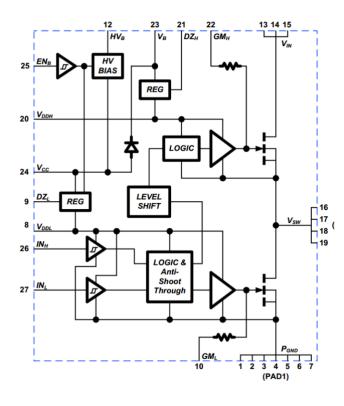

#### Two Switch ("Half-Bridge")

**GàNFast**<sup>™</sup>

- ✓ 2 x 650 V eMode FETs (Half-bridge)

- ✓  $R_{DS(ON)}$  120-500m $\Omega$  available

- ✓ Symmetric and Asymmetric R<sub>DS(ON)</sub>

- ✓ Integrated Gate Drive

- ✓ Shoot-through Protection

- ✓ Integrated Regulators

- ✓ Integrated Level-Shifter

- ✓ Integrated Boot-strap

## Integrated Drive → Simple & Robust

**GaNFast**<sup>™</sup>

## Voltage Slew Rate Control ... Easy EMI Tuning GaNFast

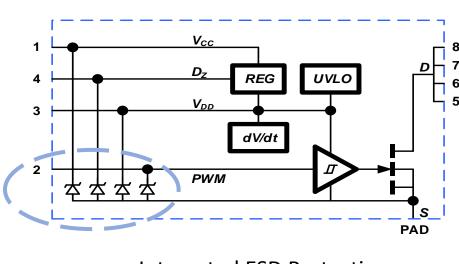

## **Integrated ESD Protection**

Integrated ESD Protection

GaN Power IC

HBM, CDM > 1,000 V

#### ESD Qualification Tests

| Reference   | Test Conditions          | Duration | Lots | S.S. |

|-------------|--------------------------|----------|------|------|

| JS-001-2014 | Human Body Model ESD     | N/A      | 1    | 3    |

| JS-002-2014 | Charged Device Model ESD | N/A      | 1    | 3    |

$\checkmark\,$  Same ESD testing as Si devices can be applied to GaN

✓ Latch up testing not required in GaN devices

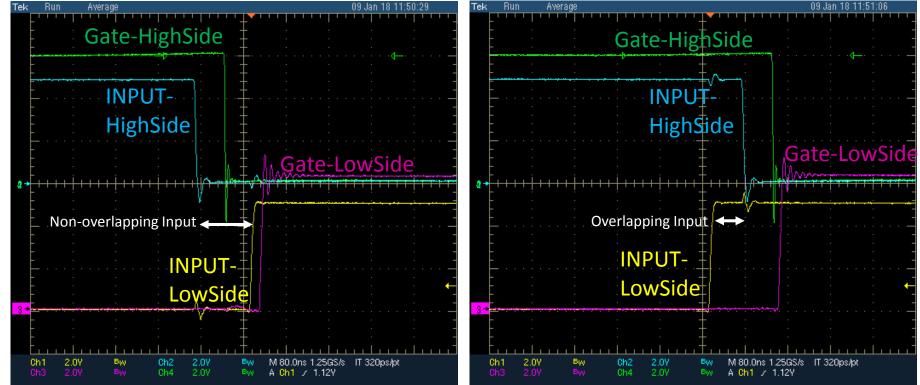

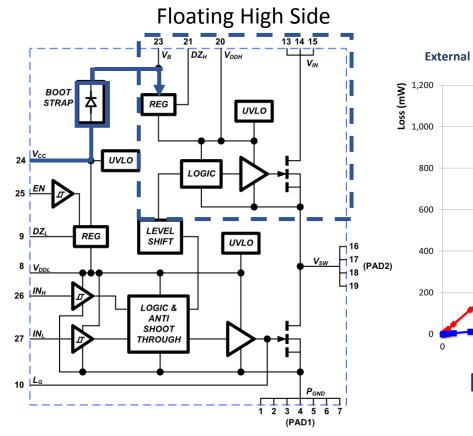

## **Shoot-Through Protection in Half-Bridge**

#### Half-Bridge GaN Power IC

Non-Overlapping Logic Input (Typical Operation) **Overlapping** Logic Input (Power IC Protection Mode)

**GaNFast**™

High-side and Low-side gates never overlap due to shoot-through protection in power IC

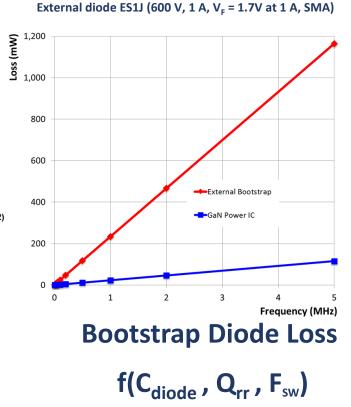

## **Integrated Bootstrap**

https://www.onsemi.com/pub/Collateral/ES1J-D.PDF

#### **Bootstrap Diode Integration Benefits:**

- Avoids risk of dV/dt induced diode failure

- Eliminates diode Cj and Irr power loss

- Eliminates necessity of using SiC at high F<sub>sw</sub>

- Saves cost, especially if SiC is required

- Charges bootstrap capacitor losslessly

- Assures full charge/voltage is delivered

- Eliminates lossy current limiting resistor

- Saves board space in HV system

## Bootstrap Startup

#### **High-side Startup Characteristics**

- Why GaN Power ICs?

- How to make GaN Power ICs?

- Features of GaN Power ICs

- Commercial requirements for GaN products

- Products using GaN Power ICs

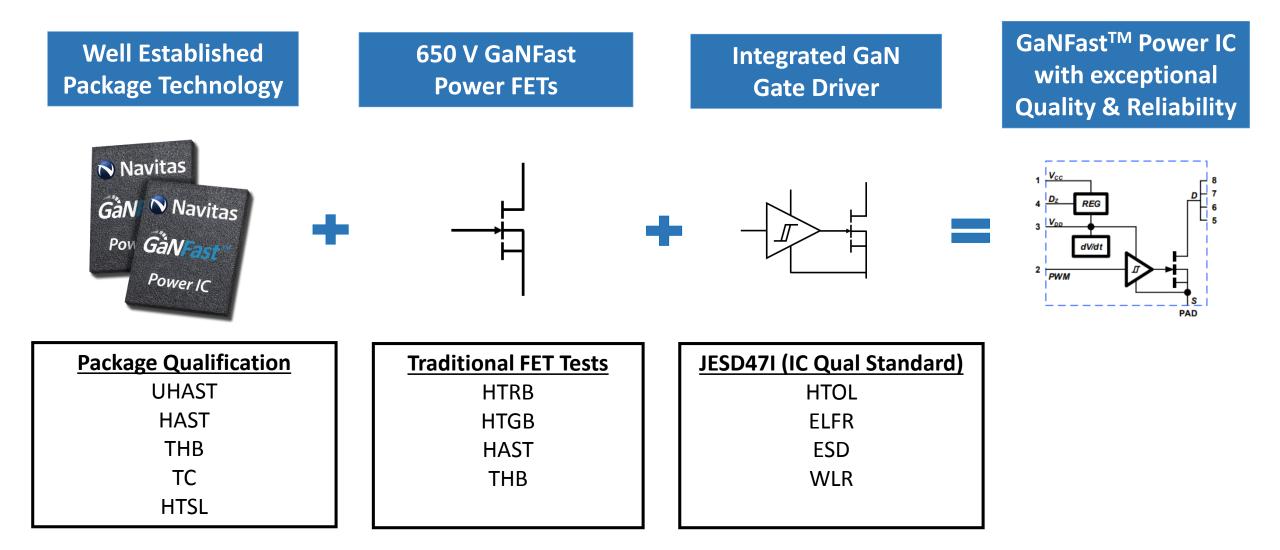

# ✓ System Value (Features, Efficiency, Density) ✓ Reliability ✓ Cost

**GàNFast**™

✓ Cost

## ✓ System Value (Features, Efficiency, Density) ✓ Reliability

**GàNFast**™

## **Approach to Reliability of GaN Power ICs**

**GaNFast**™

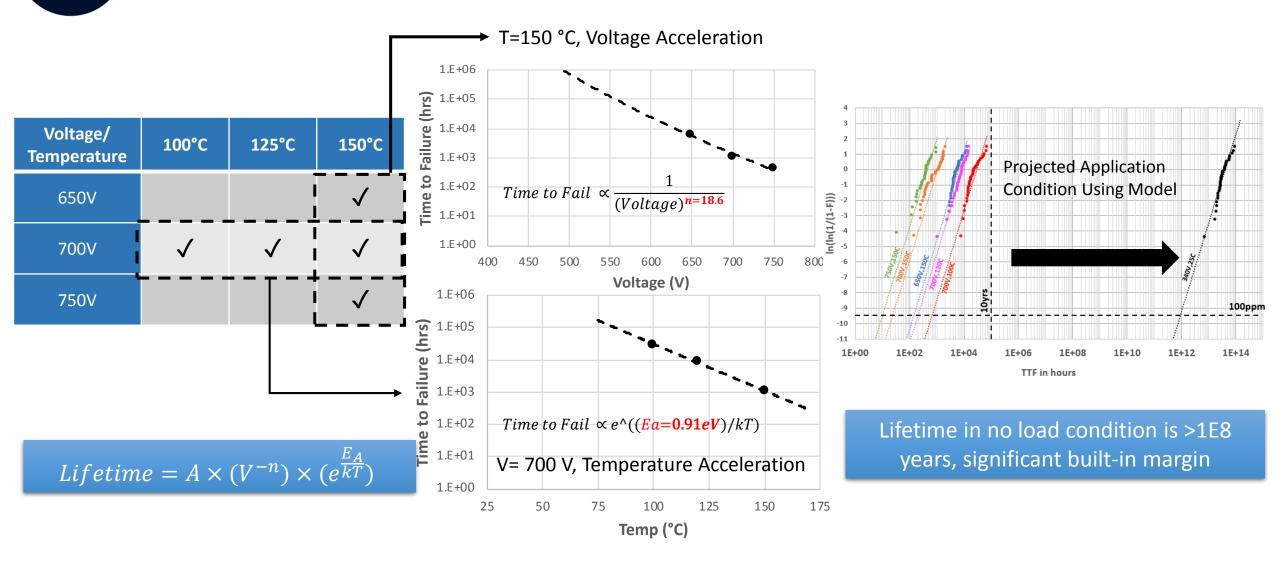

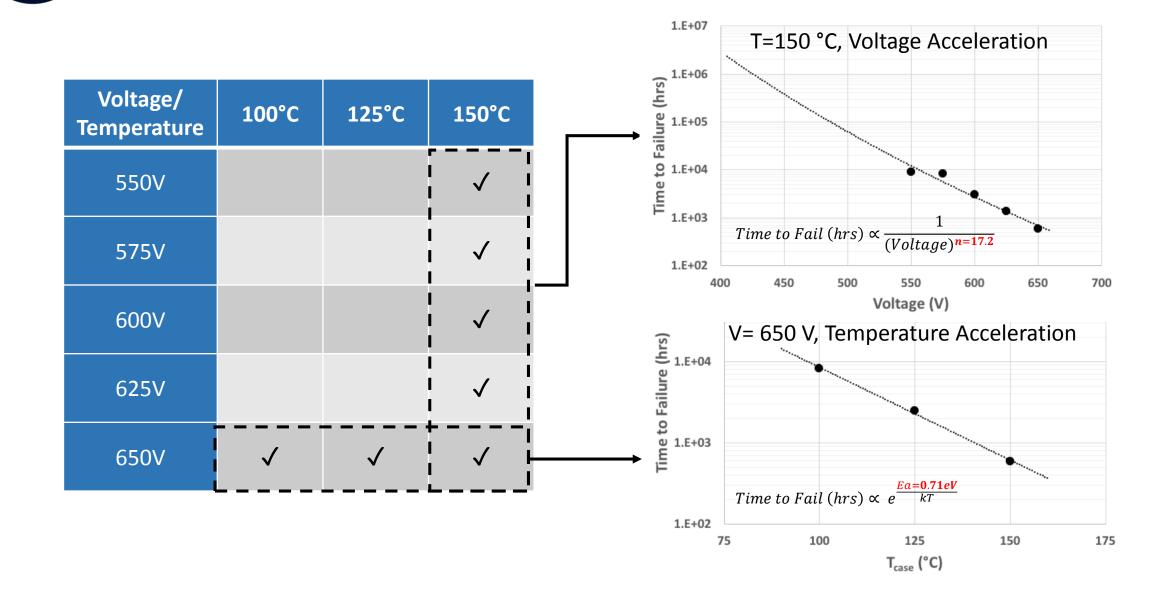

## **HTRB Acceleration & Lifetime Models**

**GaNFast**™

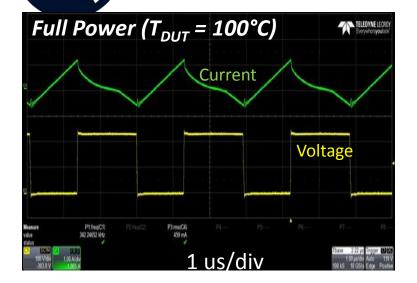

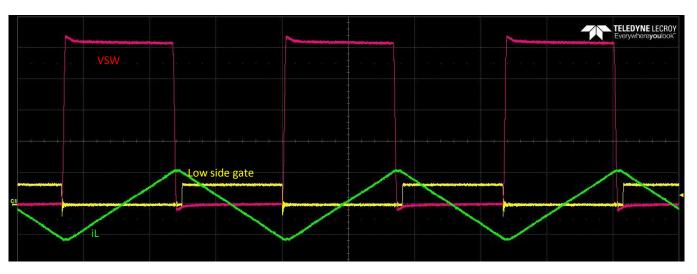

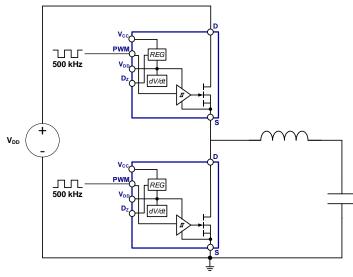

## **Mission Profile Driven HTOL (ZVS)**

ZVS test bench replicates stresses seen in ACF application

**GàNFast**™

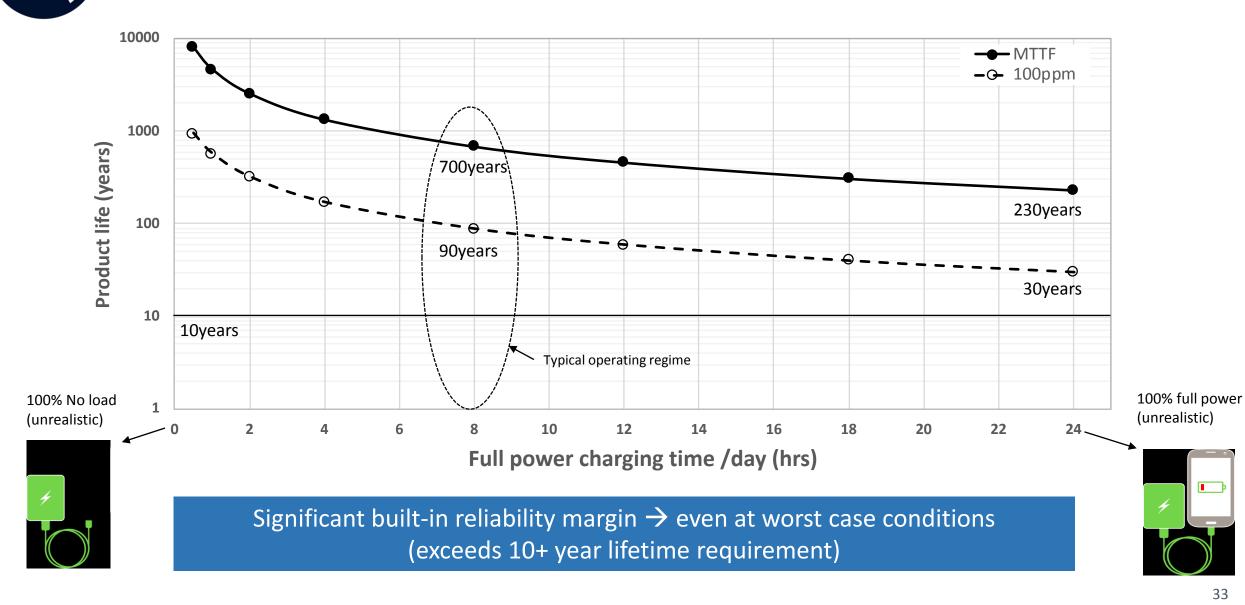

## **HTOL-based Lifetime Model**

## **Lifetime Estimation in Charger Application**

**GàNFast**™

- Why GaN Power IC?

- How to make GaN Power ICs?

- Features of GaN Power ICs

- Commercial requirements for GaN products

- Products using GaN Power ICs

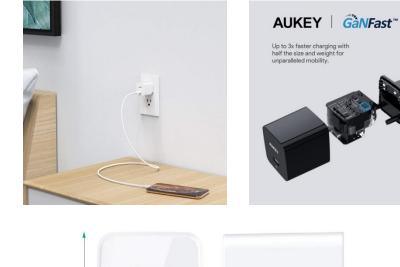

## **GaNFast USB-C Chargers Have Arrived**

#### Fast

Up to 3x more power Up to 3x faster charging

Mobile

Half the size & weight

#### Universal

One charger for *ALL* your devices *One and Done!!*

AUKEY

27W

24W

30W

45W

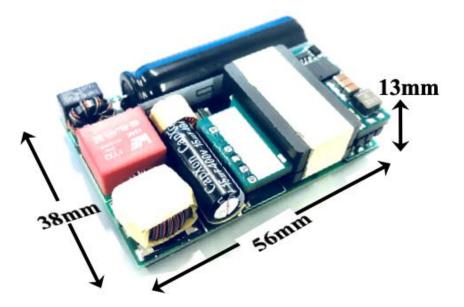

## **Latest Releases**

- World's smallest 27W USB-C

- 41.5 cc, 0.65 W/cc

- Available now from **amazon**.com

- World's smallest Charger 42W (30W-C + 18W-A) + Battery Pack (5,000 mAhr)

- 31.5 x 85.5 x 81.5 mm

- Available now from **CAPPIE Store**

## **Questions**?

## Let's go GaNFast™