## GaNFast™ Power FET

## 1. Features

## GaNFast™ Power FET

- eMode GaN power FET

- Low 120 mΩ resistance

- 10 MHz switching frequency capability

- Ultra-low gate charge

- Zero reverse recovery charge

- Low output charge

- 800 V Transient Voltage Rating

- 650 V Continuous Voltage Rating

- Source Kelvin (SK) pin for gate noise immunity

- Small, low-profile SMT DFN

- 8x8 mm PCB footprint

- Minimized package inductance

- Low thermal resistance

- Bottom-side cooled

## Environmental

- RoHS, Pb-free, REACH-compliant

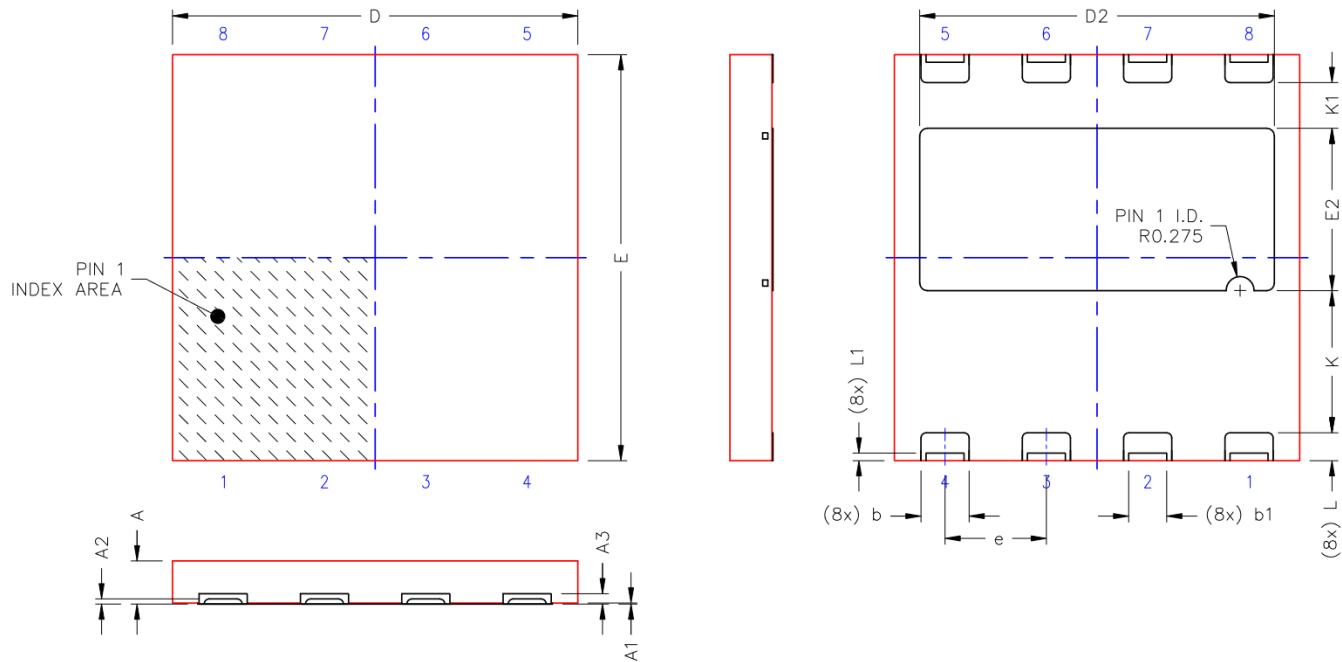

PDFN 8x8 mm

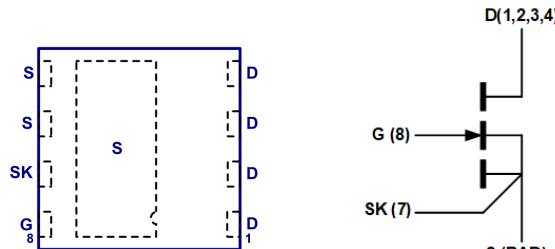

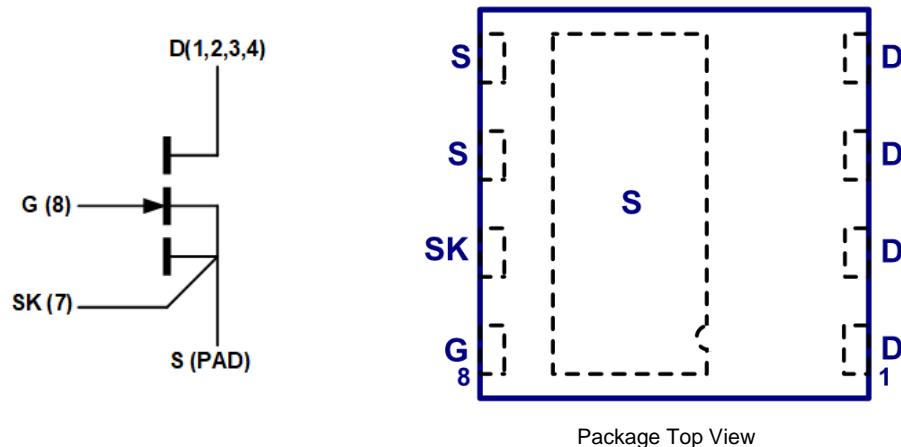

Package Outline (Top View)

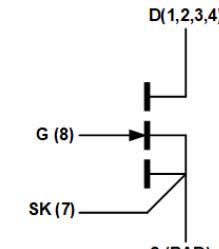

Simplified Schematic

## 2. Topologies / Applications

- AC-DC, DC-DC, DC-AC

- QR flyback, ACF, buck, boost, half bridge, full-bridge, LLC resonant, Class D, PFC

- Wireless power

- LED lighting

- Solar Micro-inverters

- TV SMPS

- Server, Telecom

## 3. Description

This GaNFast™ power FET is a high performance eMode GaN FET that achieves excellent high-frequency and high efficiency operation. Features include a simple gate input and a Source Kelvin pin for noise immunity.

This GaN power FET combines the highest dV/dt immunity and industry-standard low-profile, low-inductance, bottom-side cooled SMT QFN packaging to enable designers to achieve simple, quick and reliable solutions.

Navitas' GaN technology extends the capabilities of traditional topologies such as flyback, half-bridge, buck/boost, LLC and other resonant converters to reach MHz+ frequencies with very high efficiencies and low EMI to achieve unprecedented power densities at a very attractive cost structure.

#### 4. Table of Contents

|                                              |          |                                                        |           |

|----------------------------------------------|----------|--------------------------------------------------------|-----------|

| <b>1. Features</b> .....                     | <b>1</b> | <b>5.4. Characteristic Graphs</b> .....                | <b>5</b>  |

| <b>2. Topologies / Applications</b> .....    | <b>1</b> | <b>6. Pin Configurations and Functions</b> .....       | <b>8</b>  |

| <b>3. Description</b> .....                  | <b>1</b> | <b>7. Drain-to-Source Voltage Considerations</b> ..... | <b>9</b>  |

| <b>4. Table of Contents</b> .....            | <b>2</b> | <b>8. PDFN Package Outline</b> .....                   | <b>10</b> |

| <b>5. Specifications</b> .....               | <b>3</b> | <b>9. Ordering Information</b> .....                   | <b>11</b> |

| 5.1. Absolute Maximum Ratings <sup>(1)</sup> | 3        | <b>10. Revision History</b> .....                      | <b>11</b> |

| 5.2. Thermal Resistance                      | 3        |                                                        |           |

| 5.3. Electrical Characteristics              | 4        |                                                        |           |

## 5. Specifications

### 5.1. Absolute Maximum Ratings<sup>(1)</sup>

(with respect to Source (pad) unless noted)

| SYMBOL         | PARAMETER                                                           | MAX        | UNITS            |

|----------------|---------------------------------------------------------------------|------------|------------------|

| $V_{DS(TRAN)}$ | Transient Drain-to-Source Voltage <sup>(2)</sup>                    | 800        | V                |

| $V_{DS(CONT)}$ | Continuous Drain-to-Source Voltage                                  | -7 to +650 | V                |

| $V_{GS}$       | Continuous Gate-to-Source Voltage                                   | -10 to +7  | V                |

| $V_{TGS}$      | Transient Gate-to-Source Voltage <sup>(3)</sup>                     | -20 to +10 | V                |

| $I_D$          | Continuous Drain Current (@ $T_C = 25^\circ\text{C}$ )              | 14         | A                |

| $I_D$          | Continuous Drain Current (@ $T_C = 100^\circ\text{C}$ )             | 9          | A                |

| $I_D$ PULSE    | Pulsed Drain Current (10 $\mu\text{s}$ @ $T_J = 25^\circ\text{C}$ ) | 24         | A                |

| $P_D$          | Power Dissipation (@ $T_C = 25^\circ\text{C}$ )                     | 73         | W                |

| $dV/dt$        | Slew Rate on Drain-to-Source                                        | 200        | V/ns             |

| $T_J$          | Operating Junction Temperature                                      | -55 to 150 | $^\circ\text{C}$ |

| $T_{STOR}$     | Storage Temperature                                                 | -55 to 150 | $^\circ\text{C}$ |

(1) Absolute maximum ratings are stress ratings; devices subjected to stresses beyond these ratings may cause permanent damage.

(2)  $V_{DS(TRAN)}$  rating allows for surge ratings during non-repetitive events that are < 100us (for example start-up, line interruption).  $V_{DS(TRAN)}$  rating allows for repetitive events that are < 100ns, with 80% derating required (for example repetitive leakage inductance spikes). Refer to Section 7 for detailed recommended design guidelines.

(3) < 1  $\mu\text{s}$

### 5.2. Thermal Resistance

| SYMBOL          | PARAMETER           | TYP | UNITS              |

|-----------------|---------------------|-----|--------------------|

| $R_{eJC}^{(4)}$ | Junction-to-Case    | 1.7 | $^\circ\text{C/W}$ |

| $R_{eJA}^{(4)}$ | Junction-to-Ambient | 54  | $^\circ\text{C/W}$ |

(4)  $R_e$  measured on DUT mounted on 1 square inch 2 oz Cu (FR4 PCB)

### 5.3. Electrical Characteristics

Typical conditions:  $V_{DS} = 400$  V,  $F_{SW} = 1$  MHz,  $T_{AMB} = 25$  °C,  $I_D = 6$  A (or specified)

| SYMBOL                  | PARAMETER                                    | MIN | TYP  | MAX | UNITS | CONDITIONS                                                    |

|-------------------------|----------------------------------------------|-----|------|-----|-------|---------------------------------------------------------------|

| GaN FET Characteristics |                                              |     |      |     |       |                                                               |

| $I_{DSS}$               | Drain-Source Leakage Current                 |     | 0.3  | 25  | µA    | $V_{DS} = 650$ V, $V_{GS} = 0$ V                              |

| $I_{DSS}$               | Drain-Source Leakage Current                 |     | 25   |     | µA    | $V_{DS} = 650$ V, $V_{GS} = 0$ V, $T_c = 150$ °C              |

| $I_{GSS}$               | Gate-Source Leakage Current                  |     | 75   |     | µA    |                                                               |

| $R_{DS(ON)}$            | Drain-Source Resistance                      |     | 120  | 170 | mΩ    | $V_{GS} = 7$ V, $I_D = 6$ A                                   |

| $V_{GS(th)}$            | Gate Threshold Voltage                       | 1   | 1.7  | 2.8 | V     | $I_D = 12$ mA, $V_{DS} = 0.1$ V                               |

| $V_{SD}$                | Source-Drain Reverse Voltage                 |     | 3.2  | 5   | V     | $V_{GS} = 0$ V, $I_{SD} = 6$ A                                |

| $T_{ON}$                | Turn-On Delay Time                           |     | 4    |     | ns    | $V_{DS} = 400$ V, $V_{GS} = 5.2$ V, $I_D = 6$ A, $R_G = 10$ Ω |

| $T_{OFF}$               | Turn-Off Delay Time                          |     | 6    |     | ns    | $V_{DS} = 400$ V, $V_{GS} = 5.2$ V, $I_D = 6$ A, $R_G = 10$ Ω |

| $T_R$                   | Turn-Off Rise Time                           |     | 10   |     | ns    | $V_{DS} = 400$ V, $V_{GS} = 5.2$ V, $I_D = 6$ A, $R_G = 10$ Ω |

| $T_F$                   | Turn-On Fall Time                            |     | 5    |     | ns    | $V_{DS} = 400$ V, $V_{GS} = 5.2$ V, $I_D = 6$ A, $R_G = 10$ Ω |

| $Q_{RR}$                | Reverse Recovery Charge                      |     | 0    |     | nC    |                                                               |

| $R_G$                   | Internal Gate Resistance                     |     | 1.8  |     | Ω     |                                                               |

| $C_{ISS}$               | Input Capacitance                            |     | 75   |     | pF    | $V_{DS} = 400$ V, $V_{GS} = 0$ V                              |

| $C_{OSS}$               | Output Capacitance                           |     | 28   |     | pF    | $V_{DS} = 400$ V, $V_{GS} = 0$ V                              |

| $C_{RSS}$               | Reverse Transfer Capacitance                 |     | 0.33 |     | pF    | $V_{DS} = 400$ V, $V_{GS} = 0$ V                              |

| $Q_G$                   | Total Gate Charge                            |     | 3.3  |     | nC    | $V_{GS} = 0-6$ V, $I_D = 11.3$ A, $V_{DS} = 400$ V            |

| $Q_{GD}$                | Gate-to-Drain Charge                         |     | 0.72 |     | nC    | $V_{GS} = 0-6$ V, $I_D = 11.3$ A, $V_{DS} = 400$ V            |

| $Q_{GS}$                | Gate-to-Source Charge                        |     | 0.64 |     | nC    | $V_{GS} = 0-6$ V, $I_D = 11.3$ A, $V_{DS} = 400$ V            |

| $Q_{OSS}$               | Output Charge                                |     | 26   |     | nC    | $V_{GS} = 0$ V, $V_{DS} = 400$ V                              |

| $C_{O(er)}^{(5)}$       | Effective Output Capacitance, Energy Related |     | 43   |     | pF    | $V_{DS} = 400$ V, $V_{GS} = 0$ V                              |

| $C_{O(tr)}^{(6)}$       | Effective Output Capacitance, Time Related   |     | 64   |     | pF    | $V_{DS} = 400$ V, $V_{GS} = 0$ V                              |

(5)  $C_{O(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

(6)  $C_{O(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

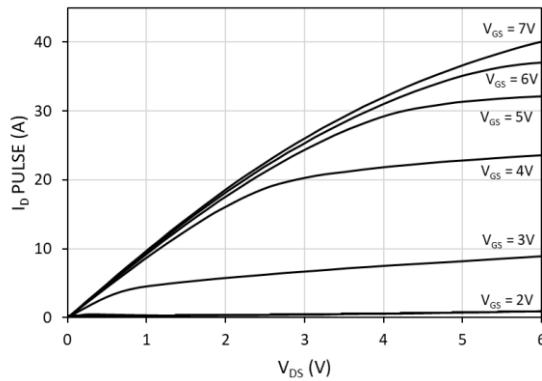

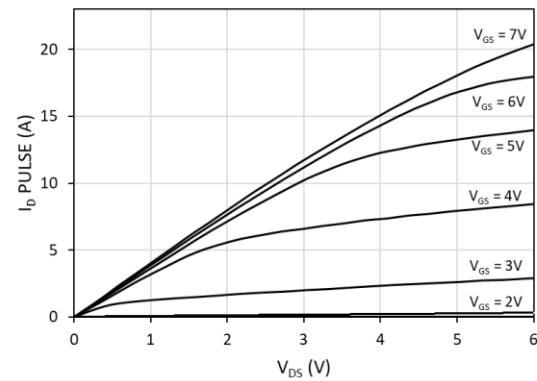

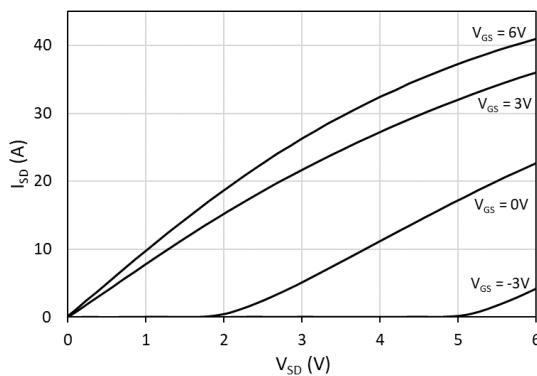

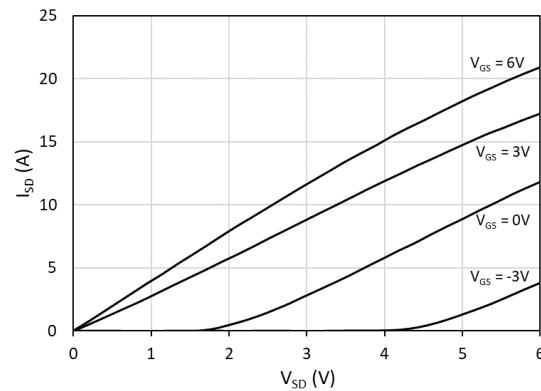

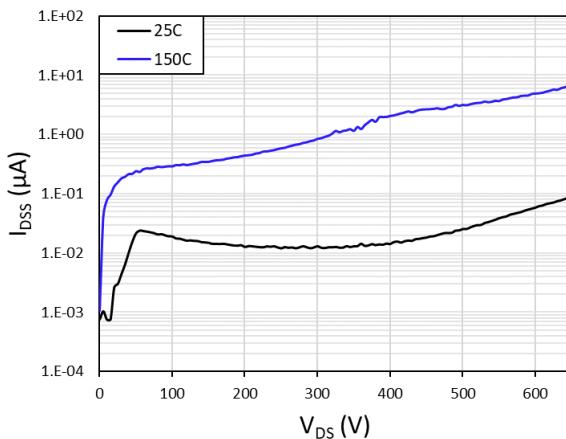

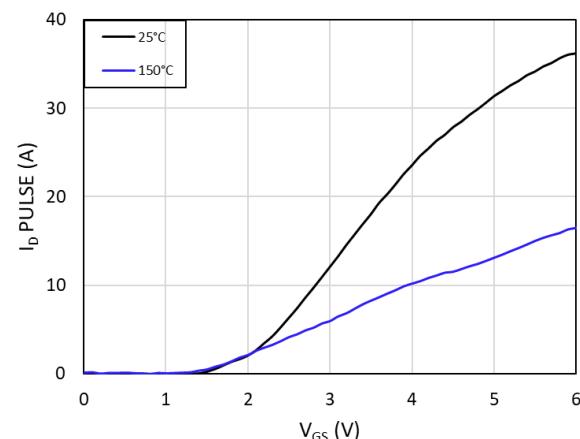

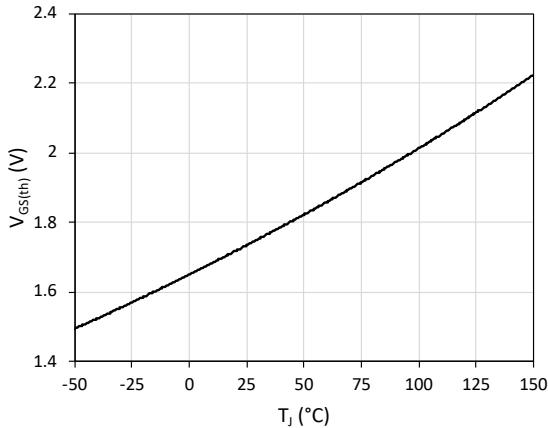

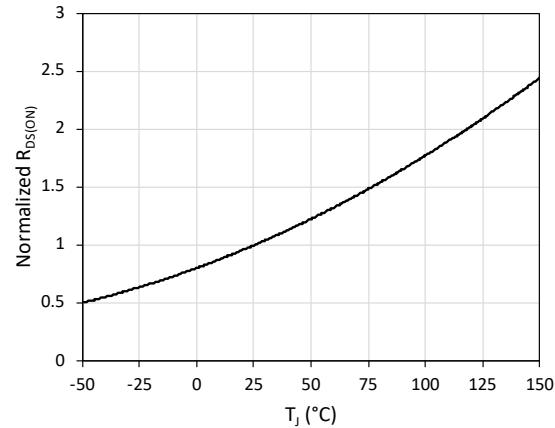

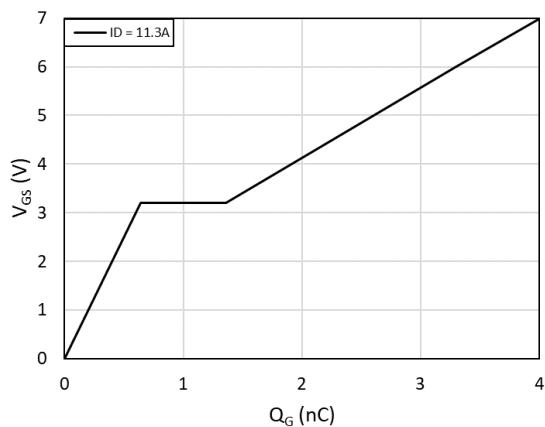

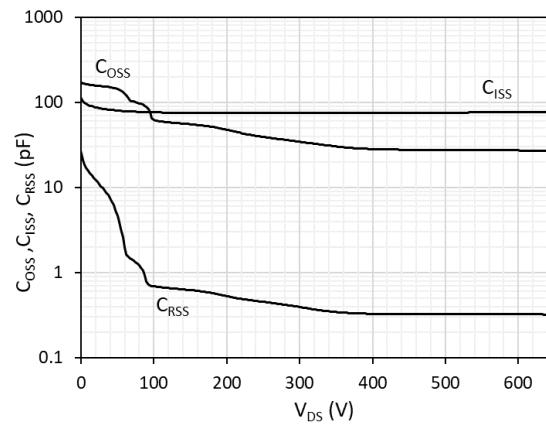

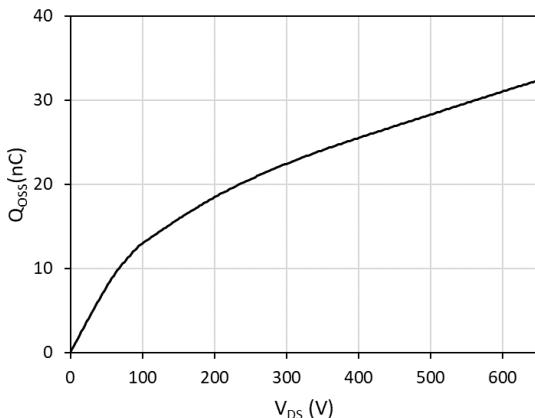

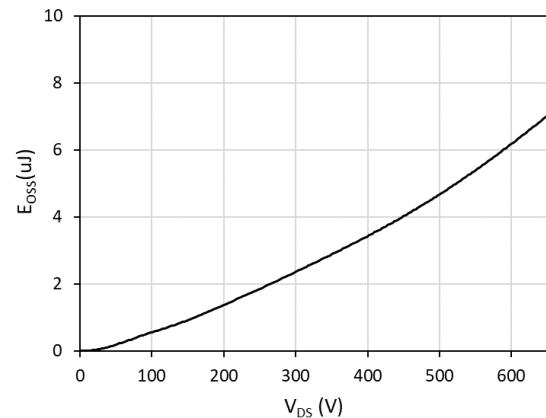

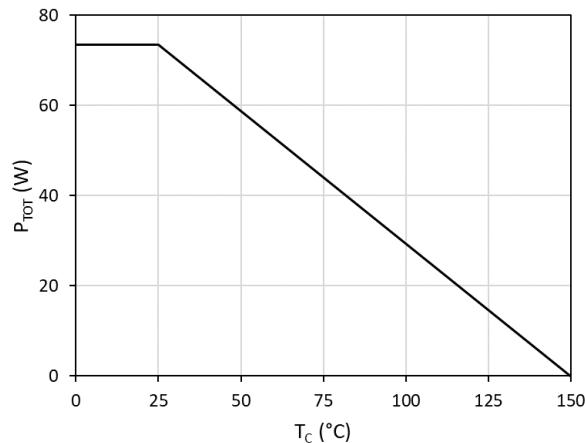

## 5.4. Characteristic Graphs

(GaN FET,  $T_C = 25^\circ\text{C}$  unless otherwise specified)

Fig. 1 Pulsed drain current ( $I_D$  PULSE) vs. drain-to-source voltage ( $V_{DS}$ ) at  $T = 25^\circ\text{C}$

Fig. 2 Pulsed drain current ( $I_D$  PULSE) vs. drain-to-source voltage ( $V_{DS}$ ) at  $T = 150^\circ\text{C}$

Fig. 3 Source-to-drain reverse conduction voltage at  $T = 25^\circ\text{C}$

Fig. 4 Source-to-drain reverse conduction voltage at  $T = 150^\circ\text{C}$

Fig. 5 Drain-to-source leakage current ( $I_{DSS}$ ) vs. drain-to-source voltage ( $V_{DS}$ )

Fig. 6 Pulsed drain current ( $I_D$  PULSE) vs. gate-to-source voltage ( $V_{GS}$ )

**Characteristic Graphs (Cont.)**

Fig. 7 Gate threshold voltage ( $V_{GS(th)}$ ) vs. junction temperature ( $T_J$ )

Fig. 8 Normalized on-resistance ( $R_{DS(ON)}$ ) vs. junction temperature ( $T_J$ )

Fig. 9 Gate-to-source voltage ( $V_{GS}$ ) vs. total gate charge ( $Q_G$ )

Fig. 10 Input capacitance ( $C_{iss}$ ), Output capacitance ( $C_{oss}$ ), Reverse Transfer capacitance ( $C_{rss}$ ), vs drain-to-source voltage ( $V_{DS}$ )

Fig. 11 Charge stored in output capacitance ( $Q_{oss}$ ) vs drain-to-source voltage ( $V_{DS}$ )

Fig. 12 Energy stored in output capacitance ( $E_{oss}$ ) vs. drain-to-source voltage ( $V_{DS}$ )

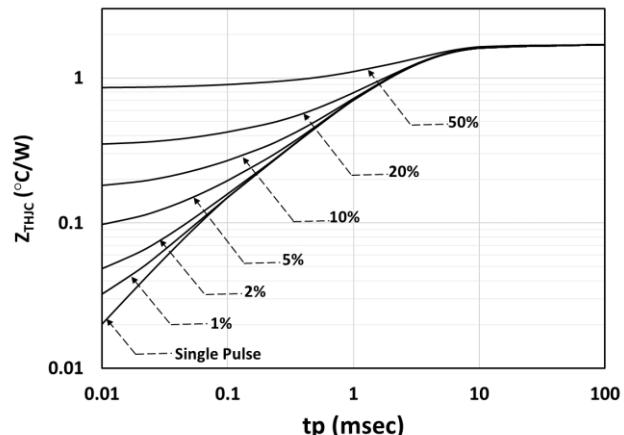

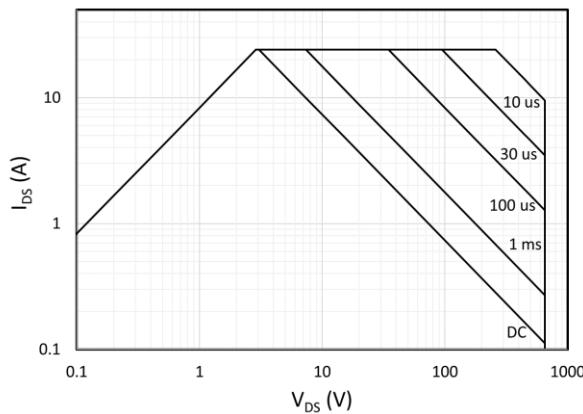

### Characteristic Graphs (Cont.)

Fig. 13 Power Dissipation (PTOT) vs case temperature

Fig. 14 Max. Thermal Transient Impedance (Z<sub>thJC</sub>) vs. Pulse Width (t<sub>p</sub>)

Fig. 15 Safe Operation Area (SOA) @ T<sub>CASE</sub> = 25°C

## 6. Pin Configurations and Functions

| Pin Number | Pin Name | Description                                           |

|------------|----------|-------------------------------------------------------|

| 5, 6       | S        | Source of power FET                                   |

| 7          | SK       | Kelvin sense of FET source. Use for driver connection |

| 8          | G        | Gate of power FET                                     |

| 1, 2, 3, 4 | D        | Drain of power FET                                    |

| PAD        | S        | Source of power FET. Metal pad on bottom of package.  |

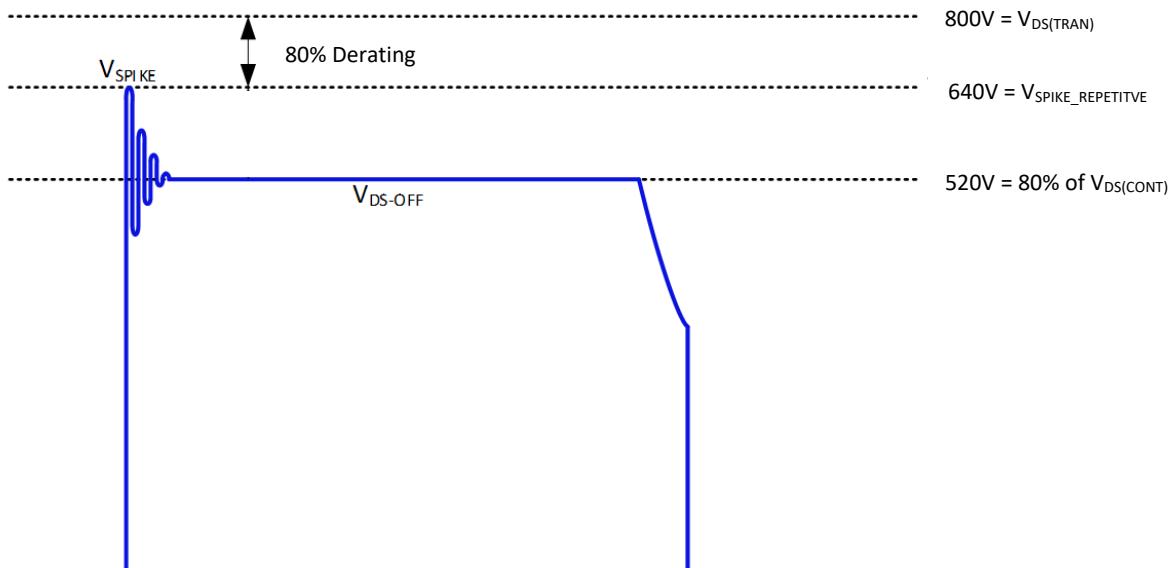

## 7. Drain-to-Source Voltage Considerations

GaN Power ICs have been designed and tested to provide significant design margin to handle transient and continuous voltage conditions that are commonly seen in single-ended topologies, such as quasi-resonant (QR) flyback applications. The different voltage levels and recommended margins in a typical QR flyback can be analyzed using Fig. 16. When the device is switched off, the energy stored in the transformer leakage inductance will cause  $V_{DS}$  to overshoot to the level of  $V_{SPIKE}$ . The clamp circuit should be designed to control the magnitude of  $V_{SPIKE}$ . After dissipation of the leakage energy, the device  $V_{DS}$  will settle to the level of the bus voltage plus the reflected output voltage which is defined in Fig. 16 as  $V_{DS-OFF}$ .

- For repetitive events, 80% derating should be applied from  $V_{DS(TRAN)}$  rating (800V) to 640V max under the worst case operating conditions.

- It is recommended to design the system such that  $V_{DS-OFF}$  is derated 80% from the  $V_{DS(CONT)}$  (650V) max rating to 520V.

- For half-bridge based topologies, such as LLC,  $V_{DS}$  voltage is clamped to the bus voltage.  $V_{DS}$  should be designed such that it meets the  $V_{DS-OFF}$  derating guideline (520V).

- Non-repetitive events are infrequent, one-time conditions such as line surge, ESD, and lightning. No derating from the  $V_{DS(TRAN)}$  rating (800V) is needed for non-repetitive  $V_{SPIKE}$  durations  $< 100 \mu s$ . The  $V_{DS(TRAN)}$  rating (800V) allows for repetitive events that are  $< 100\text{ns}$ , with 80% derating required (for example repetitive leakage inductance spikes).

Fig. 16. QR flyback drain-to-source voltage stress diagram

## 8. PDFN Package Outline

| SYM | MIN       | NOM        | MAX  |

|-----|-----------|------------|------|

| A   | 0.80      | 0.85       | 0.90 |

| A1  | 0.00      | —          | 0.05 |

| A2  | —         | 0.102 REF. | —    |

| A3  | —         | 0.203 REF. | —    |

| b   | 0.90      | 0.95       | 1.00 |

| b1  | —         | 0.75 REF.  | —    |

| D   | 7.90      | 8.00       | 8.10 |

| D2  | 6.95      | 7.00       | 7.05 |

| E   | 7.90      | 8.00       | 8.10 |

| E2  | 3.15      | 3.20       | 3.25 |

| e   | 2.00 TYP. |            |      |

| K   | —         | 2.80 REF.  | —    |

| K1  | —         | 0.90 REF.  | —    |

| L   | 0.50      | 0.55       | 0.60 |

| L1  | —         | 0.15 REF.  | —    |

### NOTES:

1. DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M – 1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS.

3. MAXIMUM ALLOWABLE BURRS IS 0.050 MM IN ALL DIRECTIONS.

## 9. Ordering Information

| Part Number | Operating Temperature Grade  | Storage Temperature Range    | Package      | MSL Rating | Packing (Tape & Reel) |

|-------------|------------------------------|------------------------------|--------------|------------|-----------------------|

| NV6027-RA   | -55 °C to +150 °C $T_{CASE}$ | -55 °C to +150 °C $T_{CASE}$ | 8 x 8 mm QFN | 3          | 1,000 : 7" Reel       |

| NV6027      | -55 °C to +150 °C $T_{CASE}$ | -55 °C to +150 °C $T_{CASE}$ | 8 x 8 mm QFN | 3          | 5,000 : 13" Reel      |

## 10. Revision History

| Date            | Status | Notes                                                                                       |

|-----------------|--------|---------------------------------------------------------------------------------------------|

| May 23, 2022    | Final  | First Publication                                                                           |

| August 22, 2022 | Final  | Add HV Timing Parameters                                                                    |

| March 7, 2024   | Final  | Add Carbon Neutral logo, PD Abs Max parameter                                               |

| Apr. 17, 2024   | Final  | Update POD, update VDSmax footnote, update Section 7 Drain-to-Source Voltage Considerations |

## Additional Information

DISCLAIMER Navitas Semiconductor (Navitas) reserves the right to modify the products and/or specifications described herein at any time and at Navitas' sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied. This document is presented only as a guide and does not convey any license under intellectual property rights of Navitas or any third parties. Navitas' products are not intended for use in applications involving extreme environmental conditions or in life support systems. [Terms and Conditions](#).

Navitas Semiconductor, Navitas, GaNFast, GaNSense and associated logos are registered trademarks of Navitas.

Copyright ©2024 Navitas Semiconductor. All rights reserved

Contact [info@navitassemi.com](mailto:info@navitassemi.com)