NV6522

DATASHEET

# GaNSafe™ Power IC

#### 1. Features

- V<sub>DS</sub> 650V continuous / 800V transient

- 55 m $\Omega$  R<sub>DS(ON)\_MAX\_25C</sub> and 41 A I<sub>DS(CONTINUOUS)</sub>

- TOLT-16L thermally-enhanced, top-cooled

- PWM input compatibility 10 to 18 V

- Paralleling capability up to 2x power ICs

- Zero reverse-recovery charge

- Turn-ON and Turn-OFF dV/dt programmability

- Up to 2 MHz operation

- Short Circuit Protection with 350 ns latency

- dV/dt immunity up to 100 V/ns

- 2kV ESD all Pins

- JEDEC and IPC-9701 Qualifications

- AEC-Q100 Grade 1 (ordering option)

- RoHS, Pb-free, REACH-compliant

## 2. Applications / Topologies

- AC-DC, DC-DC, CCM or CrM TP-PFC

- Optimized for synchronous half-bridge, fullbridge, 3-phase, or buck/boost operation

- Data Center CRPS, and Solar Inverter/ESS

- EV OBC & DC-DC converter, and motor drive

### 3. Description

The NV6522 is a thermally-enhanced top-cooled SMD version of the GaNFast™ power IC family, optimized for higher power systems using GaNSafe™ technology, making it the ideal choice for high-frequency, high-power-density, and high-efficiency power systems in data center, solar, industrial, and automotive segments.

GaNFast power ICs integrate GaN FET(s) with gate drive to create an easy-to-use power stage building block.

GaNSafe technology further integrates critical protection and performance features that enable unprecedented reliability and robustness. The TOLT package ties this architecture together with industry-standard thermally-enhanced packaging, creating dependable solutions for world-class size/weight, efficiency, and cost.

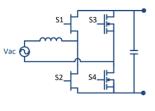

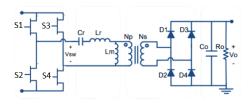

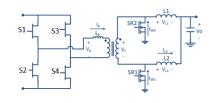

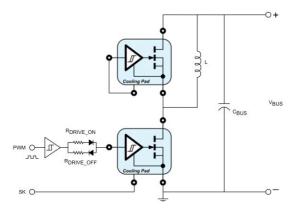

## 4. Typical Application Circuits

BTP PFC CLLC or LLC

**PSFB or DAB**

## 5. Table of Contents

| Table of Contonic                                              |             |

|----------------------------------------------------------------|-------------|

| (1) <u>Features</u>                                            | pg. 1       |

| (2) Applications / Topologies                                  | pg. 1       |

| (3) Description                                                | pg. 1       |

| (4) Typical application circuits                               | pg. 1       |

| (5) Table of contents                                          | pg. 2       |

| (6) Absolute maximum ratings                                   | pg. 3       |

| (7) Recommended operating conditions                           | pg. 4       |

| (8) ESD ratings                                                | pg. 4       |

| (9) Thermal resistance                                         | pg. 4       |

| (10) Electrical characteristics                                | pg. 5       |

| (11) Inductive switching circuit diagram                       | pg. 6       |

| (12) Electrical curves                                         | pg. 7 – 9   |

| (13) Pinout table                                              | pg. 10      |

| (14) Functional description                                    | pg. 11 – 14 |

| (14.1) GaNSafe operation                                       | pg. 11      |

| (14.2) Internal gate drive power loss                          | pg. 12      |

| (14.3) Turn-ON/OFF dV/dt control                               | pg. 12      |

| (14.4) Paralleling GaNSafe power ICs                           | pg. 12      |

| (14.5) Short Circuit Protection                                | pg. 13      |

| (14.6) Design for V <sub>DS CONT</sub> & V <sub>DS TRANS</sub> | pg. 13      |

| (14.7) PCBA layout guidelines                                  | pg. 14      |

| (14.8) PCBA reference schematic                                | pg. 15      |

| (14.9) Recommended Isolator IC's                               | pg. 15      |

| (15) Package outline dimensions                                | pg. 16      |

| (16) TnR drawing and socket orientation                        | pg. 17      |

| (17) 20-Year Limited Product Warranty                          | pg. 18      |

| (18) Ordering information                                      | pg. 18      |

| (19) Revision history                                          | pg. 18      |

Datasheet 2 Rev December 6<sup>th</sup>, 2024

## **6. Absolute Maximum Ratings**(Note 1) (with respect to Source, T<sub>CASE</sub> = 25°C, unless specified)

| Symbol                   | Parameter                                                                                                                                                   | Max         | Units |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|

| V <sub>DS(CONT)</sub>    | Continuous Drain-to-Source voltage                                                                                                                          | -7 to +650  | V     |

| V <sub>DS(TRAN)</sub>    | Transient Drain-to-Source voltage (Note 2)                                                                                                                  | 800         | V     |

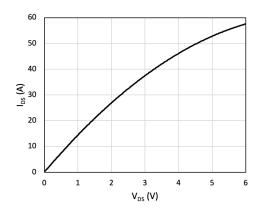

| I <sub>DS(CONT)</sub>    | Continuous Drain current (T <sub>CASE</sub> = 25 °C) (Note 3)<br>Continuous Drain current (T <sub>CASE</sub> = 100 °C, T <sub>JUNC</sub> = 150 °C) (Note 3) | 41<br>26    | А     |

| I <sub>DS_PULSE</sub>    | Pulsed Drain current (10 µs @ T <sub>JUNC</sub> = 25 °C) (Note 3)<br>Pulsed Drain current (10 µs @ T <sub>JUNC</sub> = 150 °C) (Note 3)                     | 83<br>38    | А     |

| V <sub>DRIVE_CONT</sub>  | Continuous input voltage measured between V <sub>DRIVE</sub> and SK pins                                                                                    | -0.6 to 18  | V     |

| V <sub>DRIVE_TRANS</sub> | Transient input voltage measured between V <sub>DRIVE</sub> and SK pins (Note 4)                                                                            | -2.0        | V     |

| dV/dt                    | Slew Rate on Drain-to-Source                                                                                                                                | 100         | V/ns  |

| T <sub>JUNC</sub>        | Junction Temperature                                                                                                                                        | -40 to +150 | °C    |

| T <sub>STOR</sub>        | Storage temperature                                                                                                                                         | -55 to +150 | °C    |

<sup>(1)</sup> Absolute Maximum Ratings are stress ratings, and subjecting devices to stresses beyond these ratings may cause permanent damage.

- (2)  $V_{DS\,(TRAN)}$  allows for surge ratings during *non-repetitive* events that are < 100 µs.

- (3) Limited by Short Circuit Protection.

- (4) Limited to 200 ns.

Datasheet 3 Rev December 6<sup>th</sup>, 2024

## 7. Recommended Operating Conditions (Note 5)

| Symbol                 | Parameter                                      | Min  | Тур     | Max | Units |

|------------------------|------------------------------------------------|------|---------|-----|-------|

| V <sub>DRIVE_H</sub>   | Drive input pin voltage high                   | 11   | 12 ~ 13 | 18  | V     |

| V <sub>DRIVE_L</sub>   | Drive input pin voltage low                    | -0.3 | 0       | 0.3 | V     |

| R <sub>DRIVE_ON</sub>  | Turn-ON V <sub>DRIVE</sub> Pin series resistor | 5    | 10      | 25  | Ω     |

| R <sub>DRIVE_OFF</sub> | Turn-OFF VDRIVE Pin series resistor            | 1    | 2       | 10  | Ω     |

<sup>(5)</sup> Exposure to conditions beyond maximum recommended operating conditions for extended periods of time may affect device reliability.

## 8. ESD Ratings

| Symbol | Parameter                              | Max   | Units |

|--------|----------------------------------------|-------|-------|

| НВМ    | Human Body Model (per JS-001-2014)     | 2,000 | V     |

| CDM    | Charged Device Model (per JS-002-2014) | 1,000 | V     |

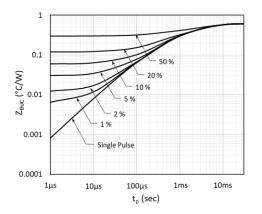

## 9. Thermal Resistance

| Symbol                   | Parameter                           | Тур  | Units |

|--------------------------|-------------------------------------|------|-------|

| R <sub>e_JUNC-CASE</sub> | Junction-to-Case Thermal Resistance | 0.60 | °C/W  |

Datasheet 4 Rev December 6<sup>th</sup>, 2024

DATASHEET

## 10. Electrical Characteristics

Conditions unless otherwise specified:  $V_{DS} = 400V$ ,  $V_{DRIVE} = 15V$ ,  $T_{CASE} = 25$ °C,  $I_{DS} = 13A$ ,  $R_{DRIVE} = 5\Omega$

| Symbol                      | Parameter                                                                    | Min  | Тур  | Max | Units | Conditions                                                                                        |

|-----------------------------|------------------------------------------------------------------------------|------|------|-----|-------|---------------------------------------------------------------------------------------------------|

| Drive Pin Ch                | aracteristics                                                                |      |      |     |       | ,                                                                                                 |

| <br>  DRIVE_OPERATING       | V <sub>DRIVE</sub> operating current                                         |      | 3.3  |     | mA    | V <sub>DRIVE</sub> = 15V, F <sub>SW</sub> = 300kHz,<br>50% D.C., V <sub>DS</sub> = 0V             |

| <br>  DRIVE_LEAKAGE         | V <sub>DRIVE</sub> leakage current                                           |      | 1.5  |     | mA    | V <sub>DRIVE</sub> = 15V                                                                          |

| Switching Cl                | haracteristics                                                               |      |      |     |       |                                                                                                   |

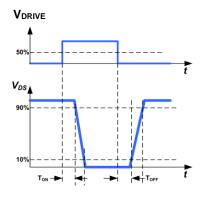

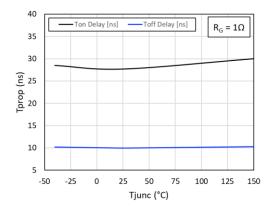

| t <sub>on</sub>             | Turn-ON propagation delay                                                    | 24   |      | 35  | ns    | Fig 1,2; -40 °C $\leq$ T <sub>CASE</sub> $\leq$ +150 °C; R <sub>DRIVE</sub> = 1 $\Omega$          |

| t <sub>OFF</sub>            | Turn-OFF propagation delay                                                   | 7    |      | 13  | ns    | Fig 1,2; -40 °C $\leq$ T <sub>CASE</sub> $\leq$ +150 °C; R <sub>DRIVE</sub> = 1 $\Omega$          |

| t <sub>ON_MIN</sub>         | Minimum valid V <sub>DRIVE</sub> on-time pulse duration (first PWM ON pulse) | 75   |      |     | ns    | $R_{DRIVE} = 5\Omega$                                                                             |

| t <sub>RISE</sub>           | Turn-OFF rise time                                                           |      | 8    |     | ns    | Fig 1,2 ; R <sub>DRIVE</sub> = 1Ω                                                                 |

| t <sub>FALL</sub>           | Turn-ON fall time                                                            |      | 7    |     | ns    | Fig 1,2 ; R <sub>DRIVE</sub> = 10Ω                                                                |

| Short Circuit               | Protection (SCP)                                                             |      |      |     |       |                                                                                                   |

| V <sub>DS_SCP</sub>         | V <sub>DS(ON)</sub> Short Circuit Detect Threshold                           | 11.5 | 13.5 |     | V     | $18V \ge V_{DRIVE} \ge 11V$ , $T_{JUNC} = -40 ^{\circ}C$ to +150 $^{\circ}C$ , verified by design |

| t<br>SCP_DLY_TURN-ON        | Delay from Short Circuit Event to Soft<br>Shut Down, into Turn-ON            |      | 350  |     | ns    | 18V ≥ V <sub>DRIVE</sub> ≥ 11V, T <sub>JUNC</sub> = -40 °C to +150 °C, verified by design         |

| t<br>SCP_DLY_OPER           | Delay from Short Circuit Event to Soft<br>Shut Down, during Operation        |      | 50   |     | ns    | 18V ≥ V <sub>DRIVE</sub> ≥ 11V, T <sub>JUNC</sub> = -40 °C to +150 °C, verified by design         |

| GaN FET Ch                  | aracteristics                                                                |      |      |     |       | , , , , , , , , , , , , , , , , , , , ,                                                           |

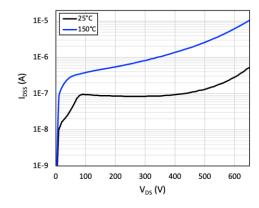

| I <sub>DSS</sub>            | Drain-Source leakage current                                                 |      | 2.0  | 100 | μA    | V <sub>DS</sub> = 650 V, V <sub>DRIVE</sub> = 0 V                                                 |

| I <sub>DSS</sub>            | Drain-Source leakage current                                                 |      | 21   |     | μΑ    | $V_{DS} = 650 \text{ V}, V_{DRIVE} = 0 \text{ V},$<br>$T_{JUNC} = 150 \text{ °C}$                 |

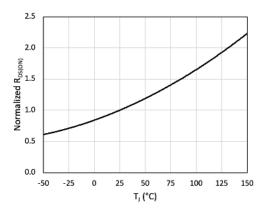

| R <sub>DS(ON)</sub>         | Drain-Source resistance                                                      |      | 40   | 55  | mΩ    | V <sub>DRIVE</sub> = 15V, I <sub>DS</sub> = 13 A                                                  |

| R <sub>DS(ON)</sub>         | Drain-Source resistance                                                      |      | 94   |     | mΩ    | V <sub>DRIVE</sub> = 15V, I <sub>DS</sub> = 13 A,<br>T <sub>JUNC</sub> = 150 °C                   |

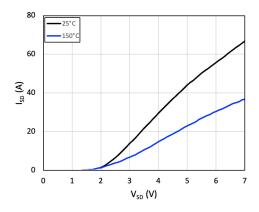

| V <sub>SD</sub>             | Source-Drain reverse voltage                                                 |      | 3.3  |     | V     | V <sub>DRIVE</sub> = 0 V, I <sub>SD</sub> = 13 A                                                  |

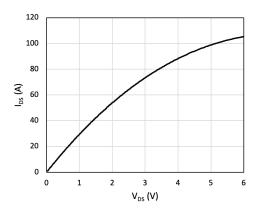

| I <sub>SD</sub>             | Source-Drain reverse current                                                 |      | 66   |     | Α     | $V_{DRIVE} = 0V$ , $V_{SD} = 7V$ , 50us pulse, based on $P_{DISSIPATION}$                         |

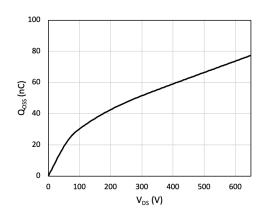

| Q <sub>oss</sub>            | Output charge                                                                |      | 59   |     | nC    | V <sub>DS</sub> = 400 V, V <sub>DRIVE</sub> = 0 V                                                 |

| $Q_{_{RR}}$                 | Reverse recovery charge                                                      |      | Zero |     | nC    |                                                                                                   |

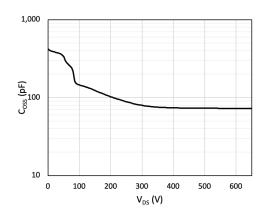

| C <sub>oss</sub>            | Output capacitance                                                           |      | 74   |     | pF    | V <sub>DS</sub> = 400 V, V <sub>DRIVE</sub> = 0 V                                                 |

| C <sub>O(er)</sub> (Note 6) | Effective output capacitance, energy related                                 |      | 99   |     | pF    | V <sub>DS</sub> = 400 V, V <sub>DRIVE</sub> = 0 V                                                 |

| C <sub>O(tr)</sub> (Note 7) | Effective output capacitance, time related                                   |      | 148  |     | pF    | V <sub>DS</sub> = 400 V, V <sub>DRIVE</sub> = 0 V                                                 |

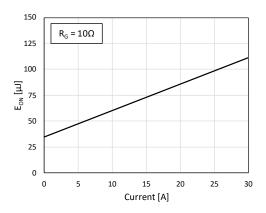

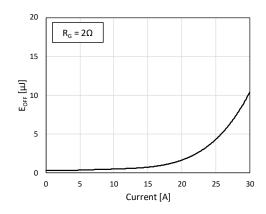

| E <sub>on</sub>             | Switching energy, Turn-ON                                                    |      | 67   |     | μJ    | $V_{DS} = 400 \text{ V}, I_{DS} = 13 \text{ A},$ $R_{DRIVE} = 10\Omega$                           |

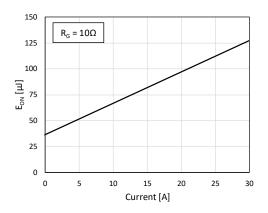

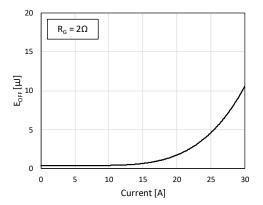

| E <sub>OFF</sub>            | Switching energy, Turn-OFF                                                   |      | 0.5  |     | μJ    | $V_{DS} = 0$ to 400 V, $I_{DS} = 13$ A, $R_{DRIVE} = 2\Omega$                                     |

|                             | II.                                                                          |      |      | •   | •     | •                                                                                                 |

<sup>(6)</sup>  $C_{O(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V

<sup>(7)</sup>  $C_{O(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 400 V Datasheet

5 Rev December 6<sup>th</sup>, 2024

## 11. Inductive Switching Test Circuit and Typical Waveforms

**Figure 1. Inductive Switching Test Circuit**

Figure 2. Prop Delay, Rise/Fall Time

## 12. Electrical Curves (GaN FET, T<sub>CASE</sub> = 25 °C unless otherwise specified)

Fig. 3.  $I_{DS}$  vs.  $V_{DS}$ ,  $T_{JUNC} = 25$  °C

Fig. 5.  $I_{SD}$  vs.  $V_{SD}$ ,  $T_{JUNC}$  = 25 °C, 150 °C

Fig. 7. Normalized R<sub>DSON</sub> vs. T<sub>JUNC</sub>

Fig. 4.  $I_{DS}$  vs.  $V_{DS}$ ,  $T_{JUNC} = 150$  °C

Fig. 6.  $I_{DSS}$  vs.  $V_{DS}$ ,  $T_{JUNC}$  = 25 °C, 150 °C

Fig. 8. Coss vs. VDS

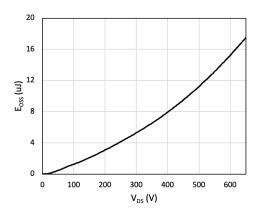

Fig. 9. Eoss vs. V<sub>DS</sub>

Fig. 11.  $t_{\mbox{\footnotesize{PROP\_ON}}\,,\,\mbox{\footnotesize{OFF}}}$  vs.  $T_{\mbox{\footnotesize{JUNC}}}$

Fig. 13. Transient  $R_{\Theta\_JUNC\text{-}CASE}$

Fig. 10.  $Q_{OSS}$  vs.  $V_{DS}$

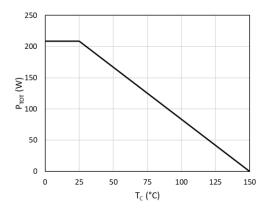

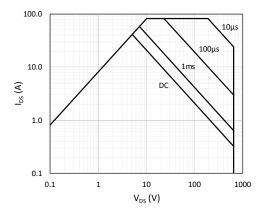

Fig. 12. PDISSIPATION VS. TCASE

Fig. 14. Safe Operating Area, T<sub>CASE</sub> = 25°C

Fig. 15. E<sub>ON</sub> vs. I<sub>DS</sub>, T<sub>JUNC</sub> = 25 °C

Fig. 17. E<sub>ON</sub> vs. I<sub>DS</sub>, T<sub>JUNC</sub> = 125°C

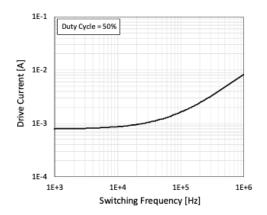

Fig. 19.  $I_{DRIVE}$  vs. Switching Frequency ( $F_{sw}$ )

Fig. 16. E<sub>OFF</sub> vs. I<sub>DS</sub>, T<sub>JUNC</sub> = 25 °C

Fig. 18. E<sub>OFF</sub> vs. I<sub>DS</sub>, T<sub>JUNC</sub> = 125°C

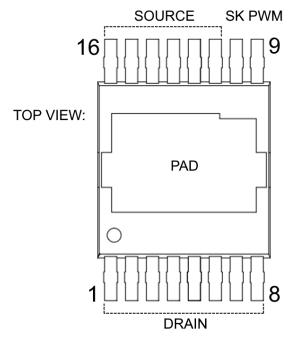

## 13. Pinout Table and P/N Marking

| Pin     | Pin                |              | Description                                                  |  |

|---------|--------------------|--------------|--------------------------------------------------------------|--|

| Number  | Symbol             | I/O (Note 8) | Description                                                  |  |

| Top Pad | Source             | G            | Source of power FET and Thermal Pad for Heatsink             |  |

| 11-16   | Source             | G            | Source of power FET                                          |  |

| 10      | SK                 | G            | Reference for isolated PWM output (Kelvin return for VDRIVE) |  |

| 9       | V <sub>DRIVE</sub> | I            | Connect isolated PWM output to VDRIVE                        |  |

| 1-8     | Drain              | Р            | Drain of power FET                                           |  |

(8) G = Ground, I = Input, P = Power

Datasheet 10 Rev December 6<sup>th</sup>, 2024

### 14. Functional Description

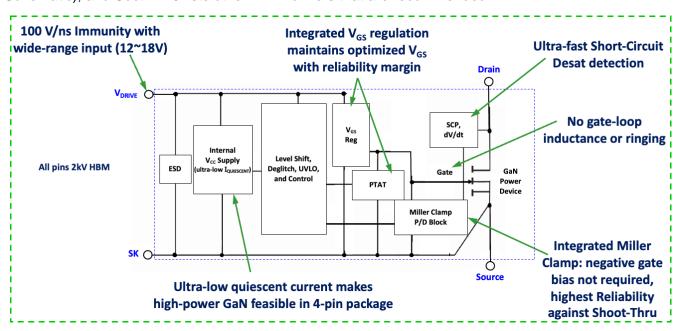

#### 14.1. GaNSafe Operation: Internally-regulated V<sub>GS</sub> and Block Diagram

GaNSafe power IC's are the industry's first GaN power devices allowing high speed operation in an industry-standard 4-Pin package (Drain / Source /  $V_{DRIVE}$  / SK) ~ also providing regulated  $V_{GS}$  and protection & performance features!

**V**<sub>DRIVE</sub> **Pin** is a patent-pending multi-function input for BOTH isolated PWM signal AND internal bias power for the GaN power IC. GaNSafe is optimized for synchronous operation under all conditions (Start-Up and Steady-State). Achieving advanced capabilities in only 4 terminals requires an isolated PWM with  $\geq$ 500mA output current and  $\geq$ 10V (**absolute minimum**). Recommended V<sub>DRIVE</sub> voltage should be  $\geq$ 11V. Typical V<sub>DRIVE</sub> voltage should be between 12V to 13V when using Bootstrap for HS device. Typical V<sub>DRIVE</sub> voltage can be up to 15V when using isolated DC-DC supply for HS device.

**Minimum On-Time:** GaNSafe power ICs have an integrated 5V power supply fed by  $V_{DRIVE}$ , and Level Shift & Deglitch circuits. The  $t_{ON\_MIN}$  (minimum valid on-time pulse at  $V_{DRIVE}$  pin) is 75ns (sect. 10).

**Internally regulated V**<sub>GS</sub> turns-ON the GaN gate with optimized voltage and turns-OFF at 0V. Negative gate bias is NOT required since there is an internal Miller Clamp to maintain the GaN gate OFF during PWM OFF state.

$V_{DS}$  Rating: During switching, the Drain toggles between Source voltage and  $V_{IN}$  (650V maximum). The Drain can withstand *non-repetitive* pulses up to 800V for <100 us [see sect. 6 for  $V_{DS(TRAN)}$  rating]. The platform design must have appropriate commutation loop decoupling and adhere to voltage margin.

Isolated PWM IC: A dual PWM driver such as SI8273BBD-IS1 can be used (see Sect. 14.8 Ref Schematic), and Sect. 14.9 lists other PWM drivers that are recommended.

Figure 20. GaNSafe Block Diagram

Datasheet 11 Rev December 6<sup>th</sup>, 2024

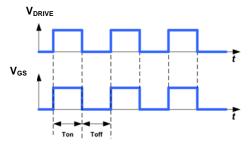

#### 14.2. Internal Gate Drive Power Loss

Internal gate drive power loss on GaNSafe power IC's can be projected by using  $I_{DRIVE}$  value from Fig. 19 ( $I_{DRIVE}$  vs.  $F_{SW}$ ), interpolated between duty cycle curves, multiplied by  $V_{DRIVE}$  (i.e.,  $I_{DRIVE}$  \*  $V_{DRIVE}$ ).

Figure 21. Normal Operating Mode Timing Diagram (VDRIVE input vs. VGS)

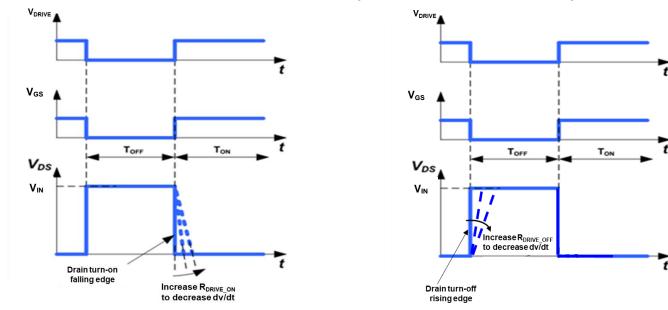

#### 14.3. Programmable Turn-ON and Turn-OFF dV/dt Control

During start-up or hard-switching condition, it may be desirable to limit slew rate (dV/dt) on the Drain. To program Turn-ON slew rate connect  $R_{DRIVE\_ON}$  in series with  $V_{DRIVE}$  pin (as shown in sect. 14.8 reference schematic). Conversely, Turn-OFF slew rate is programmed using  $R_{DRIVE\_OFF}$  series resistor value. These resistors ( $R_{DRIVE\_ON,OFF}$ ) set the *current* of the internal gate drive circuit, therefore setting dV/dt.

Figure 22. Turn-on dV/dt Slew Rate Control

Figure 23. Turn-OFF dV/dt Slew Rate Control

### 14.4. Paralleling GaNSafe power IC's

GaNSafe power IC's can be paralleled up to a recommended maximum of  $\underline{\textbf{Qtv2}}$ , maintaining close  $T_{\text{ON}}$  and  $T_{\text{OFF}}$  matching of propagation delays. The following schematic revisions should be made:

- Add Kelvin-Source resistors in the return path from each SK Pin back to the external isolated PWM driver

- Adjust R<sub>DRIVE</sub> value to assist T<sub>ON</sub> / T<sub>OFF</sub> matching

#### 14.5. Short Circuit Protection

GaNSafe power ICs continuously monitor  $V_{DS}$  and trigger Short Circuit Protection (SCP) above  $V_{DS\_SAT}$  trip point (listed in sect. 10). GaNSafe power ICs Turn-OFF via Soft Shutdown (S/D) after SCP is triggered, holding the GaN gate LOW on a cycle-by-cycle basis unless  $V_{DS\_SAT}$  setpoint is CLEARED or until the system undergoes Power-ON Reset (POR).

V<sub>DS\_SAT</sub> Min/Max tolerances (listed in sect. 10) are designed to set SCP trip point ≥20% higher than the GaN power device saturation current, up to 150C. SCP latency is 350ns including Blanking Time during Turn-ON *into* a short circuit event, but SCP latency is 50ns when a short circuit event occurs during normal switching operation.

It is critical for GaN devices to have integrated SCP (Short Circuit Protection) due to GaN's shorter SCWT (Short Circuit Withstand Time) and the need for ultra-low latency on SCP operation. However, OTP (Over Temp) & OCP (Over Current) are typically implemented via system DSP.

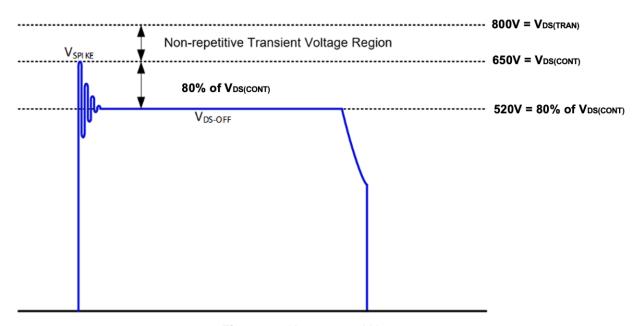

#### 14.6. Design for VDS(CONT) and VDS(TRAN)

GaNSafe power ICs have been designed and tested to provide significant design margin for continuous and transient voltage conditions, for topologies typically used in high power operation up to 22kW. These voltage levels and recommended design margin can be analyzed using Fig. 24 below. When the GaNSafe power IC is switched off, energy stored in the output circuit causes  $V_{DS}$  overshoot ( $V_{SPIKE}$ ), and after dissipation of the stored energy  $V_{DS}$  settles to the level of the bus voltage.

- For *repetitive* events, derating should be applied from V<sub>DS(TRAN)</sub> rating (800V) to V<sub>DS(CONT)</sub> rating (650V max) under the worst case operating conditions.

- It is recommended to design the system such that  $V_{DS-OFF}$  is  $\leq 520V$  (80% of  $V_{DS(CONT)}$  rating).

- Non-repetitive events are infrequent, one-time conditions such as line surge, ESD, and lightning strike. No derating from 800V is needed for non-repetitive V<sub>SPIKE</sub> durations < 100 μs.</li>

Figure 24. V<sub>DS(CONT)</sub> and V<sub>DS(TRAN)</sub>

Datasheet 13 Rev December 6<sup>th</sup>, 2024

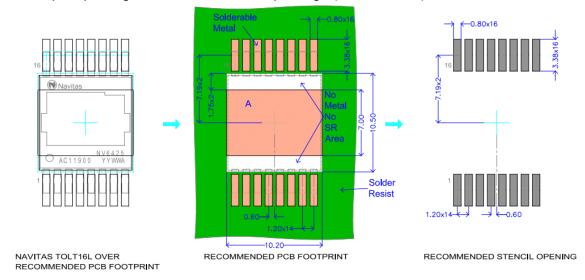

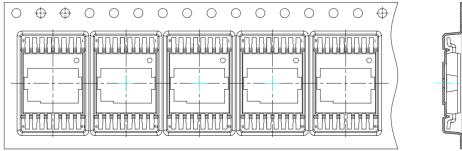

#### 14.7. PCB Layout Guidelines and PCB Footprint

PCB layout is critical for thermal management, noise immunity, and proper operation of the power IC. The following rules should be followed carefully during the design of the PCB layout:

- Place IC filter and programming components <u>directly adjacent to the GaNSafe power IC</u>, and reference all these components to the SK pin.

- Place an 0402 site for MLCC between SK and V<sub>DRIVE</sub> Pins (<u>directly adjacent to the pins</u>). This site may be stuffed with a 47pF MLCC if additional noise immunity on V<sub>DRIVE</sub> Pin is desired.

- Observe the limits on RDRIVE\_ON and RDRIVE\_OFF minimum values in ROC Sect. 7.

- Do *not* run power SOURCE currents through SK pin!

- System-level thermal design for top-cooled packages must observe co-planarity and electrical

isolation requirements when multiple power devices are cooled by the same heatsink (Cold Plate),

however, GaNSafe TOLT employs negative offset gull-wing leads to help achieve thermal pad coplanarity across multiple devices. Also, while the majority of heat is transferred thru the top-side

thermal pad, placing a Cu Plane below the package (shown below) also transfers heat to the board.

Datasheet 14 Rev December 6<sup>th</sup>, 2024

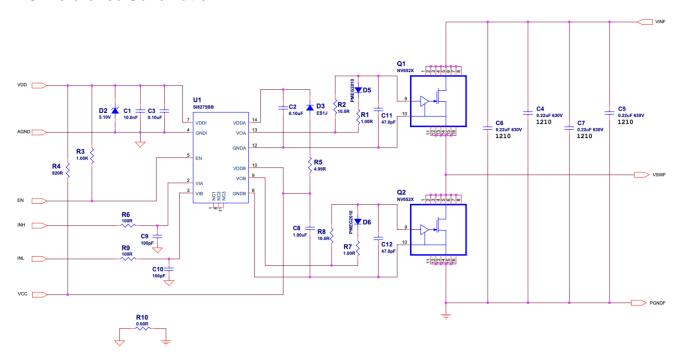

### 14.8. Reference Schematic

### 14.9. Recommended Isolator IC's:

| Supplier            | Isolated P/N     | UVLO Setpoint | CMTI (V/ns) | <b>Drive Strength</b> | Channels |

|---------------------|------------------|---------------|-------------|-----------------------|----------|

| SkyWorks (Si Labs)  | SI8273BBD-IS1    | VDDI: 1.85V   | 200         | 1.8A source/4A sink   | Dual     |

| SKY WOLKS (SI Edb3) | 310273000 131    | VDDO: 8.0V    | 200         | 1.0A 3001CC/ 4A 3111K | Duai     |

| SkyWorks (Si Labs)  | SI8275BBD-IM1    | VDDI: 1.85V   | 200         | 1 9A source/4A sink   | Dual     |

| SKYVVOTKS (SI Labs) | 2195/2000-11011  | VDDO: 8.0V    | 200         | 1.8A source/4A sink   | Duai     |

| NovoSense           | NSI6602VB-Q1SWR  | VDDI: 2.5V    | 150         | 6A source/8A sink     | Dual     |

| Novosense           | NSIDDUZVB-Q13VVK | VDDO: 8.0V    | 150         | ba source/8A sirik    | Duai     |

| NovoSense           | NCICCOOD O1CWD   | VDDI: 2.35V   | 150         | 4A course /CA sink    | Dual     |

| Novosense           | NSI6602B-Q1SWR   | VDDO: 8.0V    |             | 4A source/6A sink     | Dual     |

| ludin a a n         | 250502755        | VDDI: 2.75V   | 150         | 4.A. a.a              | Dural    |

| Infineon            | 2EDF8275F        | VDDO: 8.0V    | 150         | 4A source/8A sink     | Dual     |

| Infinan             | 150002755        | VDDI: 2.7V    | 200         | FA source /OA sink    | Cinalo   |

| Infineon            | 1EDB8275F        | VDDO: 8.0V    | 300         | 5A source/9A sink     | Single   |

Datasheet 15 Rev December 6<sup>th</sup>, 2024

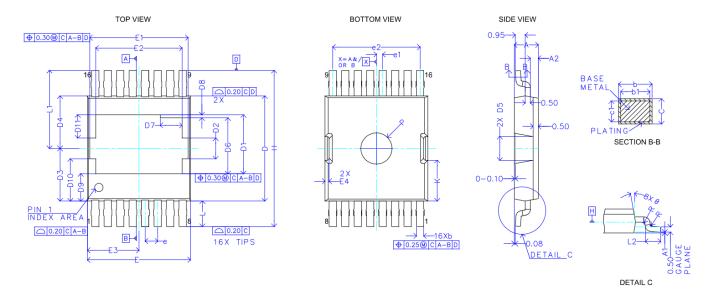

## 15. Package Outline Dimensions:

| SYMBOL | MIN   | MAX   | SYMBOL | MIN      | MAX   |

|--------|-------|-------|--------|----------|-------|

| Α      | 2.25  | 2.35  | E      | 9.70     | 10.10 |

| A1 (+) | 0.01  | 0.11  | E1     | 9.26     | 9.66  |

| A2     | 0.56  | 0.96  | E2     | 8.10     | 8.50  |

| b      | 0.60  | 0.85  | E3     | 4.75     | 5.15  |

| b1     | 0.60  | 0.80  | E4     | 0.20     | 0.60  |

| С      | 0.45  | 0.65  | е      | 1.20 BSC |       |

| c1     | 0.45  | 0.60  | e1     | 0.60 BSC |       |

| D      | 10.00 | 10.30 | e2     | 8.40 BSC |       |

| D1     | 5.47  | 5.87  | Н      | 14.80    | 15.20 |

| D2     | 1.80  | 2.20  | К      | 3.71     | 4.11  |

| D3     | 4.85  | 5.25  | L      | 2.25     | 2.65  |

| D4     | 5.00  | 5.13  | L1     | 7.30     | 7.70  |

| D5     | 2.08  | 2.48  | L2     | 1.30     | 1.70  |

| D6     | 5.17  | 5.57  | R      | 0.07     | -     |

| D7     | 1.80  | 2.20  | Р      | 2.90     | 3.10  |

| D8     | 0.10  | 0.50  | θ      | 4°       | 10°   |

| D9     | 2.42  | 2.82  |        | •        |       |

| D10    | 3.85  | 4.25  |        |          |       |

| D11    | 2.04  | 2.44  |        |          |       |

|        |       |       |        |          |       |

Datasheet 16 Rev December 6<sup>th</sup>, 2024

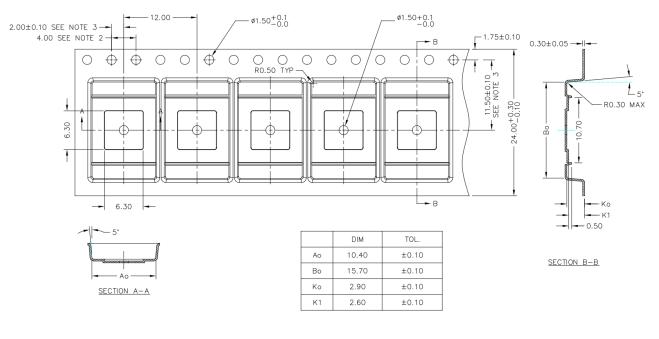

## 16. TnR Drawing and Socket Orientation

Datasheet 17 Rev December 6th, 2024

## 17. 20-Year Limited Product Warranty

A 20-year limited warranty applies to packaged Navitas GaNSafe power ICs in mass production, subject to the terms and conditions of Navitas' express limited product warranty (available at <a href="https://navitassemi.com/terms-conditions">https://navitassemi.com/terms-conditions</a>). The warranted specifications include only the MIN and MAX values listed only in Table 6 (Absolute Maximum Ratings), Table 8 (ESD Ratings), and Table 10 (Electrical Characteristics) of this datasheet. Typical (TYP) values or other specifications are not warranted.

18. Ordering Information

| Part Number | Qualification     | Package        | MSL Rating | TnR Sizes/Qtys              |

|-------------|-------------------|----------------|------------|-----------------------------|

| NV6522      | JEDEC             |                |            | Standard (13" dia) Qty1,500 |

| NV6522-RA   | JEDEC             | TOLT-16L       | 0          | Mini-Reel (7" dia) Qty450   |

| NV6522Q     | AEC-Q100 Grade 1  | Top-cooled SMD | 3          | Standard (13" dia) Qty1,500 |

| NV6522Q-RA  | -40 °C to +125 °C |                |            | Mini-Reel (7" dia) Qty450   |

19. Revision History

| 13. INCVISION IN            | Story  |                                                               |

|-----------------------------|--------|---------------------------------------------------------------|

| Date                        | Status | Notes                                                         |

| Feb 23 <sup>rd</sup> , 2024 | Final  | First Datasheet Publication                                   |

| Jul 1 <sup>st</sup> , 2024  | Final  | Updated Sect. 14 Applications, Sect. 7 ROC Table, and Fig. 18 |

| Aug 1 <sup>st</sup> , 2024  | Final  | Updated V <sub>DRIVE</sub> ratings on Pages 1, 3, 4, and 11   |

| Sep 17 <sup>th</sup> , 2024 | Final  | Added Trise and Trall to the Electrical Characteristics table |

| Dec 6 <sup>th</sup> , 2024  | Final  | Updated Sect. 14.9 Recommended Isolator IC part numbers       |

|                             |        |                                                               |

#### **Additional Information**

EXCEPT TO THE EXTENT THAT INFORMATION IN THIS DATA SHEET IS EXPRESSLY AND SPECIFICALLY WARRANTED IN WRITING BY NAVITAS SEMICONDUCTOR ("NAVITAS"), EITHER PURSUANT TO THE TERMS AND CONDITIONS OF THE LIMITED WARRANTY CONTAINED IN NAVITAS' STANDARD TERMS AND CONDITIONS OF SALE OR A WRITTEN AGREEMENT SIGNED BY AN AUTHORIZED NAVITAS REPRESENTATIVE, (1) ALL INFORMATION IN THIS DATA SHEET OR OTHER DESIGN RESOURCES PROVIDED BY NAVITAS, INCLUDING WITHOUT LIMITATION RELIABILITY AND TECHNICAL DATA, REFERENCE DESIGNS, APPLICATION ADVICE OR TOOLS, AND SAFETY INFORMATION (COLLECTIVELY, "DESIGN RESOURCES"), ARE PROVIDED "AS IS" AND WITH ALL FAULTS; AND C1) NAVITAS MAKES NO WARRANTIES OR REPRESENTATIONS AS TO ANY SUCH INFORMATION OR DESIGN RESOURCES AND HEREBY DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

**CUSTOMER RESPONSIBILITIES.** This data sheet and other Design Resources provided by Navitas are intended only for technically trained and skilled developers designing with Navitas- or GeneSiC-branded products ("Products"). Performance specifications and the operating parameters of Products described herein are determined in the independent state and may not perform the same way when installed in customer products. The customer (or other user of this data sheet) is solely responsible for (a) designing, validating and testing the application, products and systems in which Products are incorporated; (b) evaluating the suitability of Products for the intended application and the completeness of the information in this data sheet with respect to such application; (c) ensuring the application meets applicable standards and any safety, security, regulatory or other requirements; (d) procuring and/or developing production firmware, if applicable; and (e) completing system qualification, compliance and safety testing. EMC testing, and any automotive, high-reliability or other system qualifications that apply.

**NON-AUTHORIZED USES OF PRODUCTS.** Except to the extent expressly provided in a writing signed by an authorized Navitas representative, Products are not designed, authorized or warranted for use in extreme or hazardous conditions; aircraft navigation, communication or control systems; aircraft power and propulsion systems; air traffic control systems; military, weapons, space-based or nuclear applications; life-support devices or systems, including but not limited to devices implanted into the human body and emergency medical equipment; or applications where product failure could lead to death, personal injury or severe property or environmental damage. The customer or other persons using Products in such applications without Navitas' agreement or acknowledgement, as set forth in a writing signed by an authorized Navitas representative, do so entirely at their own risk and agree to fully indemnify Navitas for any damages resulting from such improper use.

CHANGES TO, AND USE OF, THIS DATA SHEET. This data sheet and accompanying information and resources are subject to change without notice. Navitas grants you permission to use this data sheet and accompanying resources only for the development of an application that uses the Products described herein and subject to the notices and disclaimers above. Any other use, reproduction or display of this data sheet or accompanying resources and information is prohibited. No license is granted to any Navitas intellectual property right or to any third-party intellectual property right.

**TERMS AND CONDITIONS.** All purchases and sales of Products are subject to <u>Navitas' Standard Terms and Conditions of Sale</u>, including the limited warranty contained therein, unless other terms and conditions have been agreed in a writing signed by an authorized Navitas representative. This data sheet, and Navitas' provision of this data sheet or other information and resources, do not expand or otherwise alter those terms and conditions.

Navitas, GeneSiC, the Navitas and GeneSiC logos, GaNFast, GaNSafe and other Navitas marks used herein are trademarks or registered trademarks of Navitas Semiconductor Limited or its affiliates. Other trademarks used herein are the property of their respective owners.

Copyright © 2024 Navitas Semiconductor Limited and affiliates. All rights reserved.

Datasheet 19 Rev December 6<sup>th</sup>, 2024