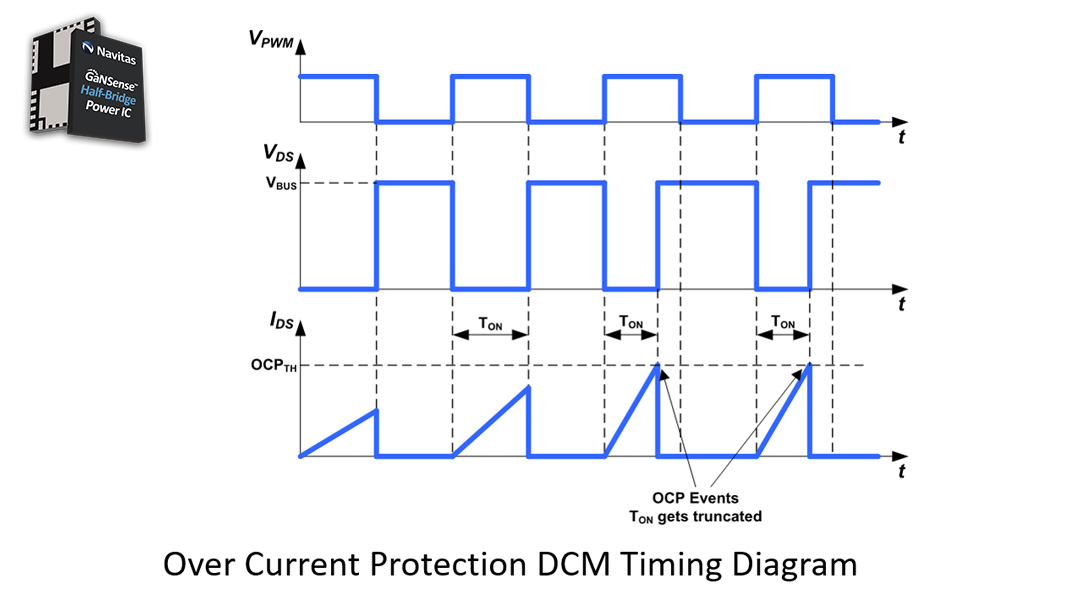

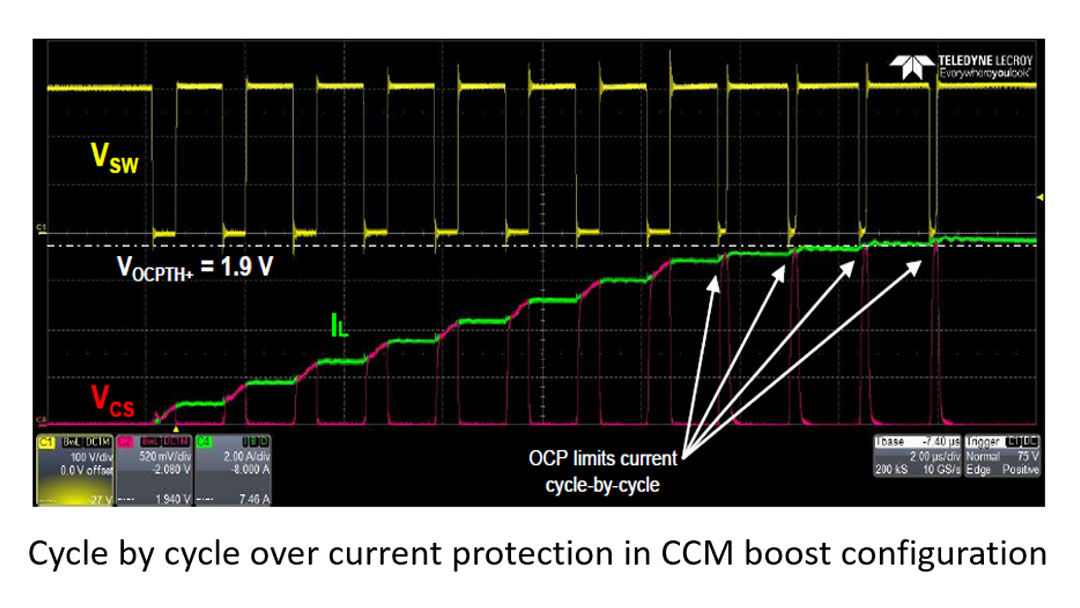

During the on-time of each low-side switching cycle (INH = low, INL = high), should the peak current exceed the internal OCP threshold, then the internal low-side gate drive will turn the low-side GaN power FET off quickly and truncate the low-side on-time period to prevent damage from occurring to the IC.

The internal OCP threshold (1.9 V, typical) is much higher than OCP thresholds of many popular PWM controllers. This ensures good compatibility of this IC with existing controllers without OCP threshold conflicts.

Find out more in our whitepaper and Application Note AN018: