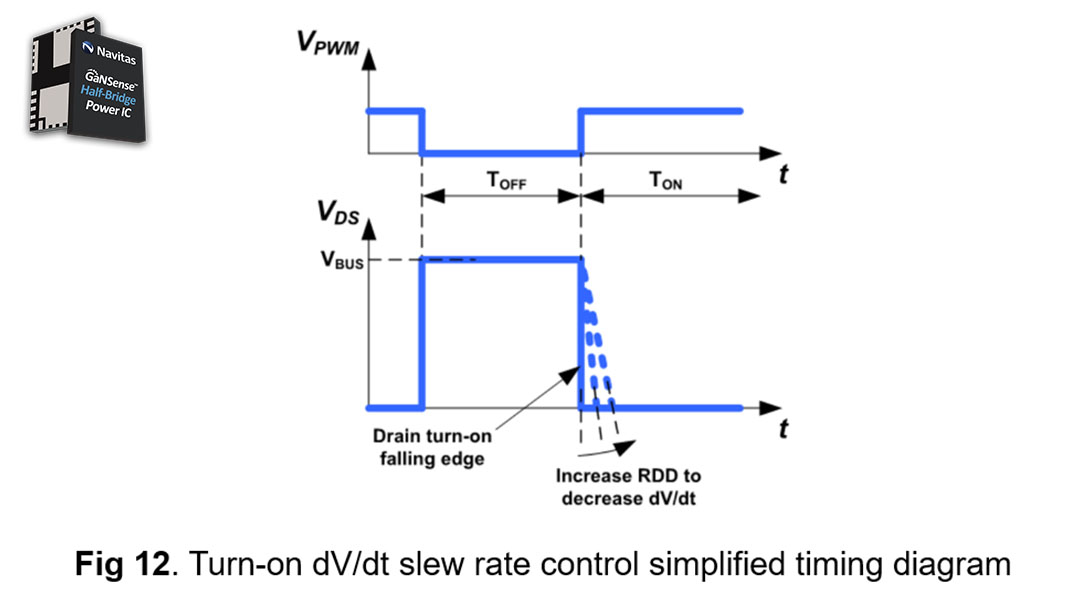

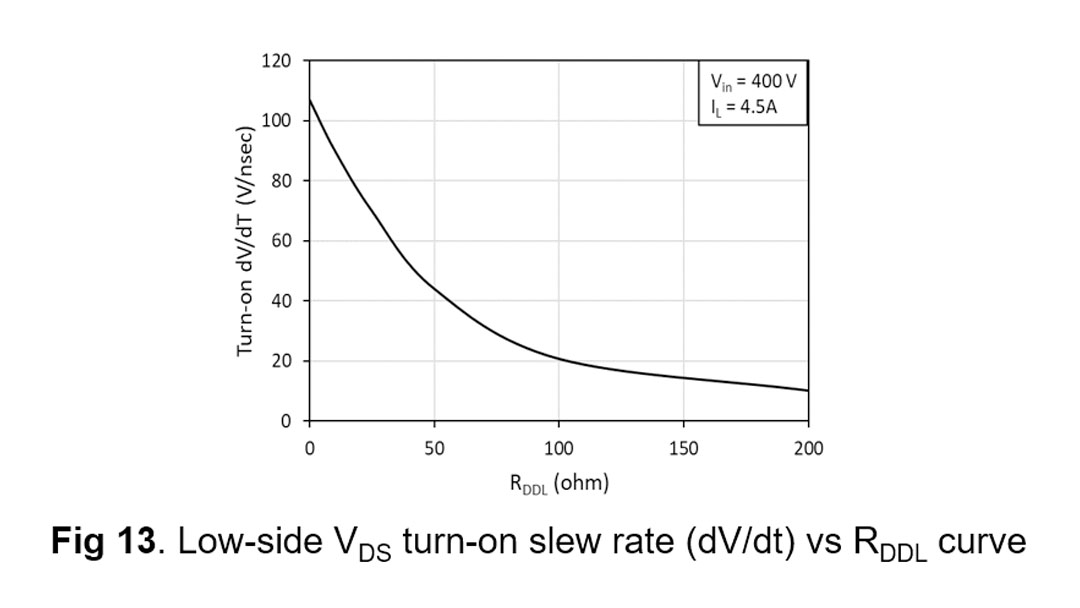

During first start-up pulses or during hard-switching conditions, it is desirable to limit the slew rate (dV/dt) of the drain of the low-side GaN power FET during turn-on. This is necessary to reduce EMI or reduce circuit switching noise.

To program the turn-on dV/dt rate of the low-side GaN power FET, a resistor is placed between the VDDL pin and the RDDL pin. This resistor sets the turn-on current of the internal gate driver and therefore sets the turn-on falling edge dV/dt rate of the drain of the low-side GaN power FET

Find out more in our whitepaper and Application Note AN018: