Unlocking GaN’s Full Potential

![27_Pdf_File_Type_Adobe_logo_logos-512[1]](https://navitassemi.com/wp-content/uploads/2020/12/27_Pdf_File_Type_Adobe_logo_logos-5121.png)

Unlocking GaN’s Full Potential

By Tom Ribarich, Sr. Dir. Strategic Marketing

GaN ICs simplify designs, improve performance and boost robustness & reliability

Introduction

Hidden Resonant Parasitic Network

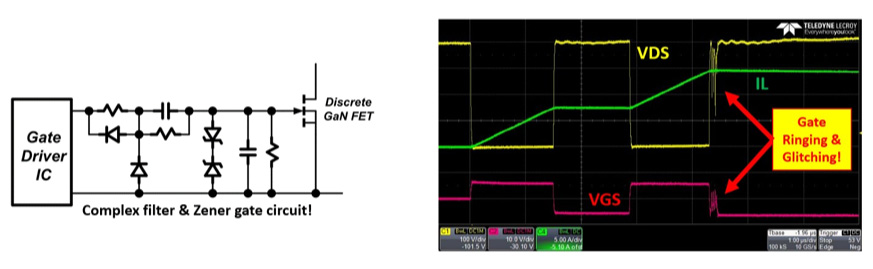

For enhancement-mode (eMode, normally off) discrete GaN FETs, a high level of sensitivity exists at the gate due to a low threshold voltage and a narrow gate voltage operating range. To make things worse, there is a ‘hidden’ resonant network of parasitic resistors, inductors and capacitors around the FET formed by the PCB, GaN FET package, and GaN device itself. An example of this parasitic resonant network consists of a discrete GaN FET mounted on a standard FR4 PCB (Figure 1a). This ‘deceptively simple’ circuit seems like it will easily work for generating the necessary square-wave gate voltage. A more detailed ‘extracted’ circuit including parasitics reveals a much more complex network surrounding the discrete GaN FET. PCB material, PCB copper traces, GaN FET package leadframe and wirebonds, and external component parasitics all form parasitic resistors, inductors and capacitors at the gate, drain and source. The intrinsic capacitors of the GaN FET device itself (CGS, CGD, CDS) also form part of the parasitic network.

(a) Discrete GaN FET on PCB and ‘hidden’ parasitic resonant network with switching current paths

(b) Complex filter and Zener gate circuit, and, gate voltage ringing and glitching waveforms

Figure 1: Discrete GaN FET on PCB, parasitic resonant network, and ringing & glitching waveforms

This parasitic resonant network becomes excited during each dV/dt switching transition of the drain voltage causing currents to flow around various parasitic resonant circuit loops. These resonant currents (Figure 1a) will cause excessive voltage spikes and ringing to occur at different parasitic circuit nodes, including the gate of the GaN FET. During turn-on, a negative dV/dt occurs at the drain node causing current to flow into the gate node and through CGD to the drain. During turn-off, a positive dV/dt occurs at the drain node causing current to flow through CGD and out of the gate node. The external gate drive signal itself will also excite the gate and source loop parasitics.

All of these switching conditions will cause voltage spikes and ringing (Figure 1b) at the gate that will turn the discrete GaN FET on or off unexpectedly (glitching) and can cause poor reliability, reduced lifetime or destruction of the GaN FET. These constraints make these devices very susceptible to high-frequency and high dv/dt noise from the surrounding switched-mode converter circuit. To mitigate these problems, external components are placed at the gate that include a gate capacitor to filter the voltage spikes, a series capacitor and Zener diodes to generate positive and negative gate voltage levels, and additional resistors to help dampen the gate ringing induced by the gate loop inductance (Figure 1b). Adding external components will not completely eliminate these problems due to component tolerances, temperature variation, and internal package parasitics, so the internal gate of the device can still have spikes and ringing even if the external gate pin waveform looks clean. Also, the gate is still exposed on the PCB making it always susceptible to external voltage surges and transients, or dV/dt occurring elsewhere in the circuit, creating high risk for field failures. Dealing with all these problems, while trying to increase switching frequency and increase power density, can be a major roadblock to bringing a product out of the lab, into production, and into the field. A simpler and more reliable solution is needed without adding additional design difficulties or robustness concerns.

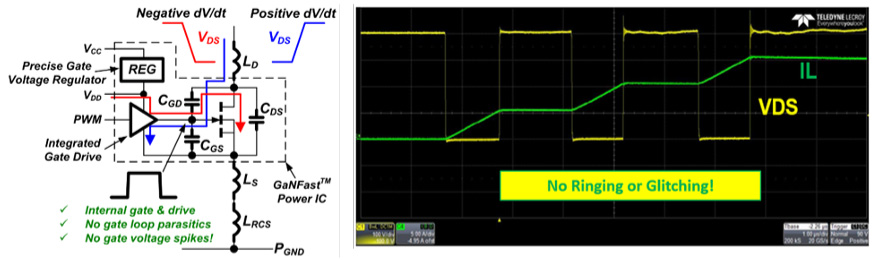

Integrate the Gate

(a) GaNFastTM technology highlights (b) Switching waveforms (Boost CCM, Fsw = 400kHz)

Figure 2: GaNFastTM Power IC with integrated gate, no gate loop parasitics, and no ringing or glitching

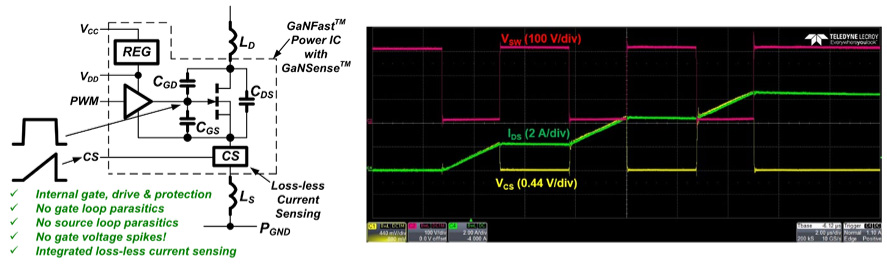

GaNSenseTM Technology

(a) GaNSenseTM technology highlights sensing (b) No ringing or glitching and clean current waveforms (Boost CCM, Fsw = 200kHz)

Figure 3: GaNSenseTM technology integrates loss-less current sensing and eliminates source loop parasitics

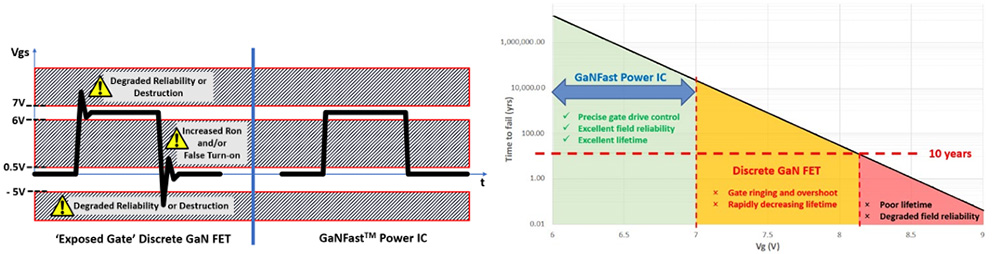

Avoid the Danger Zones!

Figure 4: Gate voltage danger zones and gate votage vs lifetime graph

Conclusion

References (www.navitassemi.com)

1) GaNFast NV6123, NV6125, NV6127 datasheets, Navitas Semiconductor, 2019

2) GaNFast NV613x/NV615x Power ICs with GaNSense Technology datasheets, Navitas Semiconductor, 2021